對便攜式電子設備的需求增加導致需要發展尺寸進一步縮小的高效能邏輯器件。然而,當互補金屬氧化物半導體(CMOS)晶體管中SiO2柵介質的尺寸進一步縮小時,諸如柵極漏電流的問題會出現。將Si CMOS技術在低熱預算前提下規模化生產的一類方法是采用具有高介電常數(κ)的材料作為柵介質,這種方法能降低單個晶體管的等效氧化層厚度(EOT)和工作電壓(Vdd)。目前而言,最先進的Si金屬氧化物半導體場效應晶體管(MOSFETs)(例如Intel開發的14nm FinFET結構)采用了厚度為2.6 nm的HfO2柵介質,對應的EOT為0.9 nm。此外,低待機功率CMOS需要的臨界柵極漏電流和界面態密度(Dit)分別為1.5 × 10?2 A?1 cm2和~1010cm?2 eV?1。

另一種在超小MOSFETs中減少柵極漏電流和與此相關的熱耗散問題——短溝道效應(SCEs)的方法是減小溝道厚度。SCEs出現對應的特征溝道長度與下式有關:

其中tch(εch) 和tox (εox)分別為溝道、柵氧化物的厚度(介電常數),N為柵的個數。因此,2D半導體,特別是寬帶隙的過渡金屬硫族化合物(TMDs),已被廣泛研究用作低功耗電子器件的溝道材料。然而,對于EOT為亞1 nm、柵極漏電流以及界面質量與Si CMOS等同的高κ柵介質,將其與2D材料集成仍具挑戰性。這主要是因為介電材料在沉積到2D材料(一般無懸掛鍵)上時,會產生非均勻成核。

2D材料上進行的原子層沉積(ALD)通常通過在缺陷、邊緣、雜質處的隨機成核進行,最后形成多孔薄膜。過去十年,為了實現高κ氧化物在2D材料上的均勻沉積,許多界面活化層和處理過程相繼出現,例如基于氧化金屬層,有機分子,BN,臭氧,輕度等離子體處理,電子束刻蝕等的工藝。然而,這些方法都有其特定的不足。例如,廣泛使用的金屬氧化過程遺留了蒸鍍金屬薄膜過程中的較大粗糙度,也存在高能金屬離子帶來的損傷。采用臭氧、等離子體、電子刻蝕的過程也涉及高能和高反應性的物質,這些都可能引入缺陷和界面態。

采用分子晶種層的方法則難以在整個器件區域實現無缺陷和精準厚度控制。剝離的BN被證明是2D材料的理想柵介質,但其較低的介電常數導致其柵極漏電流遠高于國際半導體技術藍圖(國際半導體技術藍圖)所立標準;此外,其對準轉移過程也難以量產。對于基于石墨烯和TMDs的晶體管而言,至今所報道的最小EOTs值分別為1.3和2.5 nm。另外,研究也報道了一種柵介質轉移策略,用于將高質量柵介質集成到2D材料,但這個方法通常涉及不常用的軟光刻技術,與現有的半導體制造工藝尚未兼容。

對于低功率邏輯應用而言,2D材料上的界面緩沖層必須滿足嚴格的標準。首先,界面層的厚度必須接近單層極限(ML),因為更大的厚度值將降低柵電容,使得EOT值不太可能接近1 nm。其次,界面層必須在納米尺度上緊密堆積、在微米尺度上具有均勻性,以避免柵介質上出現小孔。第三,界面緩沖層與2D材料之前的相互作用應是非共價型,以維持2D材料和界面的本征性質。最后,相關工藝必須強穩、可規模化,以實現大面積CVD薄膜。

基于以上考慮,南京大學王欣然教授聯合王鵬教授開發了一種將超薄高κ介電層集成到石墨烯、BN以及TMDs上的技術。

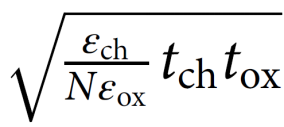

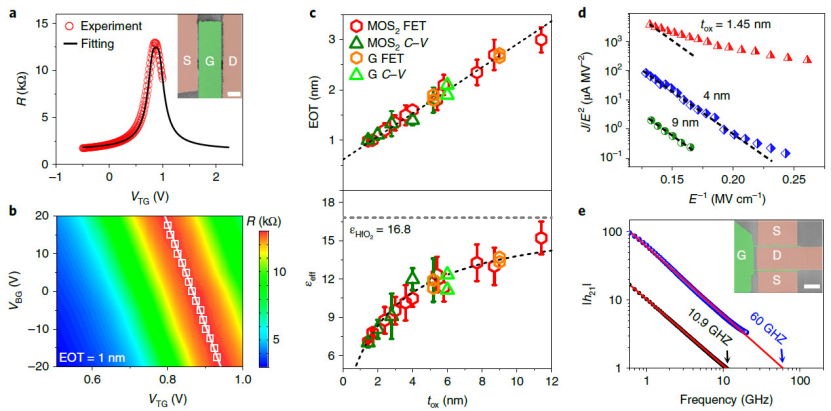

圖1. 超薄高k值氧化物在2D材料上的沉積。

本文要點

1. 該方法采用3,4,9,10-苝四酸二酐(PTCDA)分子晶體作為ALD制備介電層的晶種層,其中PTCDA非共價結合于2D材料。通過自限外延生長,分子晶體的厚度可以減小到單層極限(~0.3 nm)。

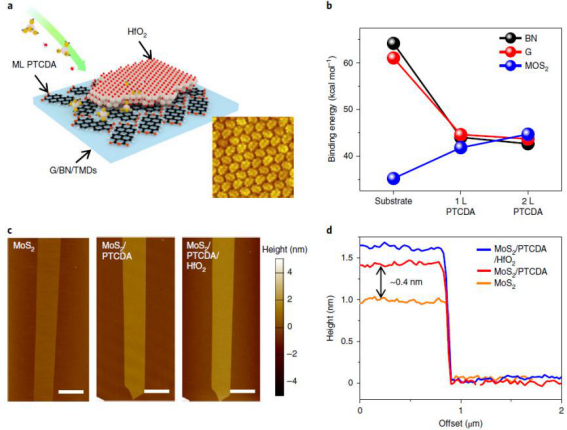

圖2. 柵疊層的STEM表征

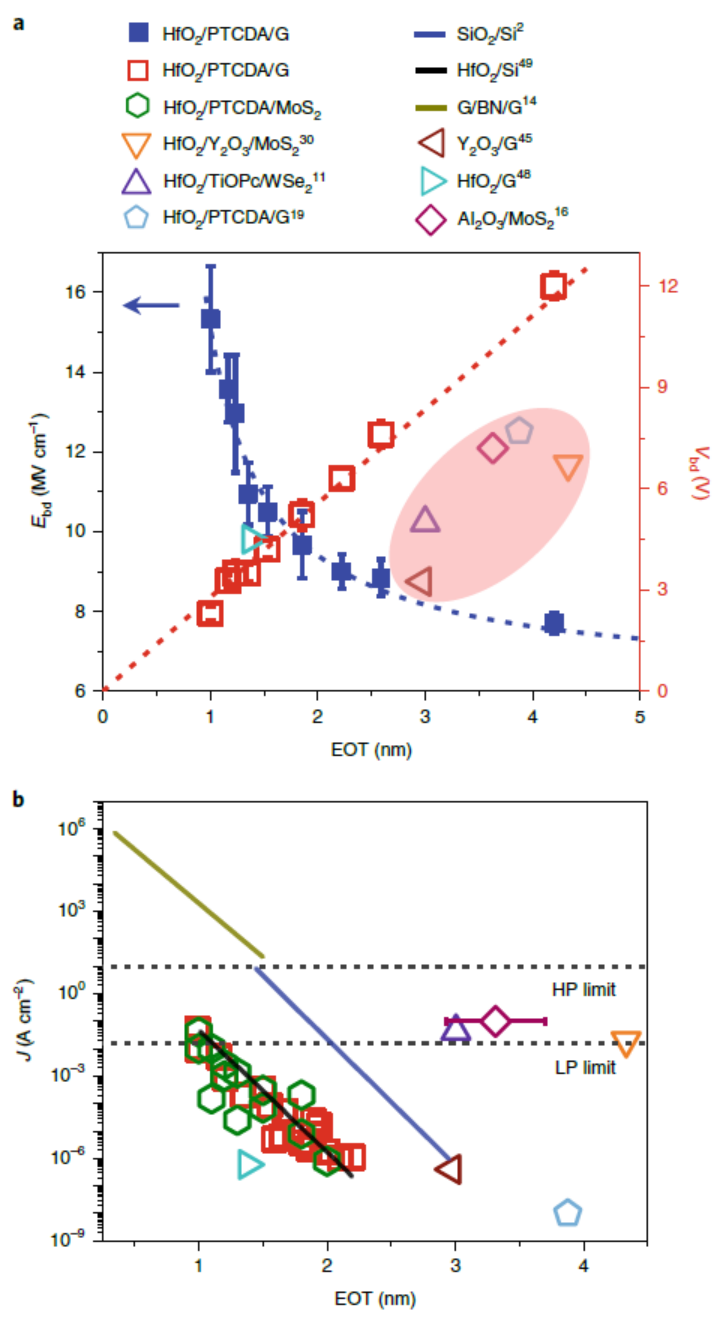

2. 利用該技術,作者在不犧牲介電性能的前提下,在石墨烯和MoS2上實現了1nm 的EOT值(tox=1.45 nm)。PTCDA/HfO2柵介質表現出低柵極漏電流(J<10?2A?1 cm2)和高擊穿電場(Ebd =16.5 MV cm?1)(對應1 nm EOT)。這些性能達到ITRS對于低功率器件的要求。

圖3. 石墨烯FETs上的介電性質。

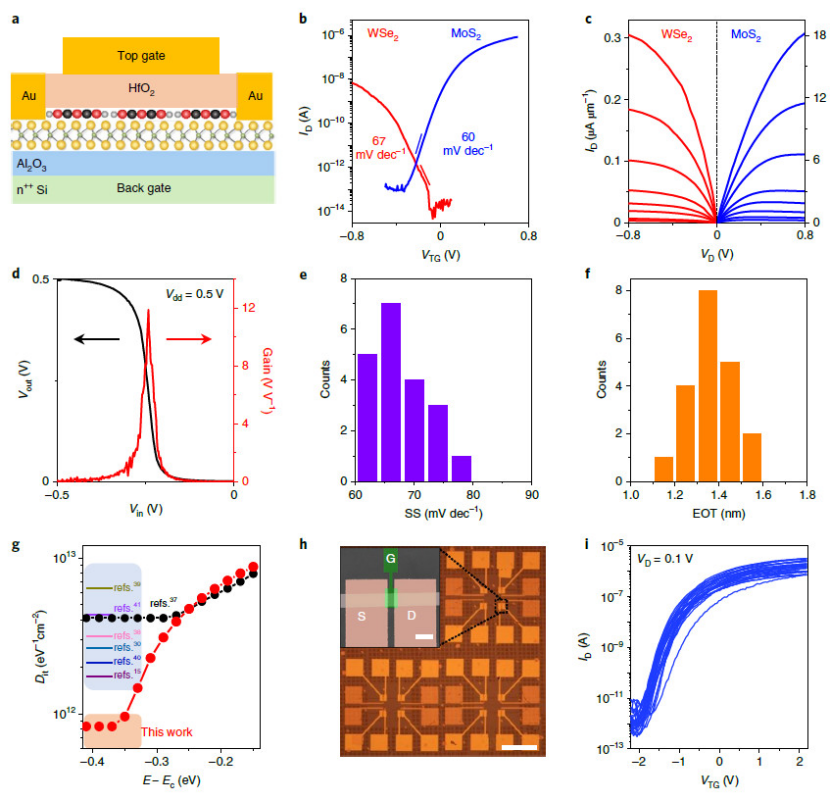

圖4. 低功耗 TMD CMOS

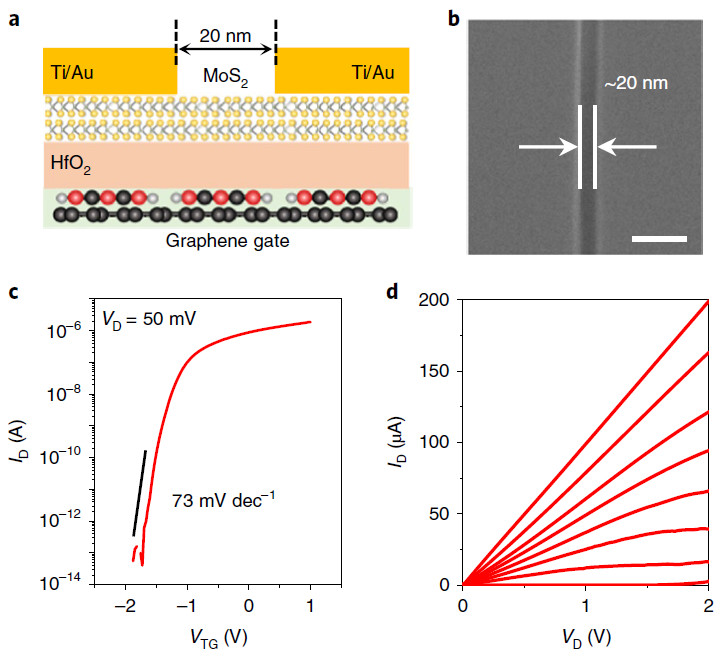

3. 在此基礎上,作者組裝了頂柵MoS2 FETs,其Dit值較小。EOT和Dit較小進一步使得MoS2/WSe2 CMOS晶體管的Vdd變小,達到目前最先進的Si CMOS的水平;開關比超過106,亞閾值擺幅分別為60 和67 mV dec-1。進一步,作者制造了20-nm溝道的MoS2晶體管,其開關比超過107,亞閾值擺幅為77 mV dec-1。最后,作者將ML PTCDA/HfO2生長于CVD制備的大面積MoS2薄膜上,采用自上而下工藝制備了晶體管陣列,后者具有很好的產率和重復性。

圖5. 短溝道MoS2 FETs

展望

基于本文工作,作者提出了以下展望:

1. 采用εox值更大的氧化物,例如ZrO2 (εox= 35),可能在tox=1.5 nm實現0.77 nm的EOT。但要注意,在保持厚度和均勻性不變的條件下,若要實現更小的EOT值,需要介電常數k更大的晶種層。

2. 為實現高性能集成電路,需要更潔凈的CVD生長技術,轉移工藝,以及制造過程,以使表面雜質最少。

圖6. 其他技術對應的擊穿和漏電流性能方面的紀錄

參考文獻:

Li, W., Zhou, J., Cai,S. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensionalelectronic devices. Nat Electron (2019) doi:10.1038/s41928-019-0334-y

https://www.nature.com/articles/s41928-019-0334-y