第一作者:吳凡、田禾、沈陽

通訊作者:任天令、田禾

通訊單位:清華大學

主要內容

對于下一代電子器件的發展,超小尺度的晶體管受到廣泛關注。雖然目前相關文獻報道了原子層MoS2厚度晶體管,制備小于1 nm的晶體管器件仍是個非常巨大的挑戰課題。

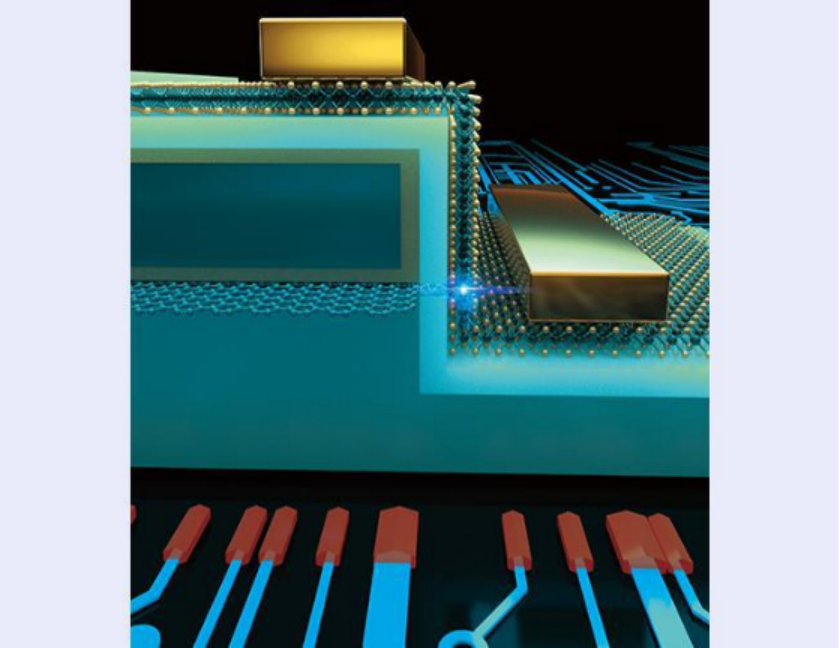

有鑒于此,清華大學集成電路學院任天令、田禾等報道實現了原子層厚度溝道的垂直MoS2晶體管器件,通過石墨烯作為柵極電極,首次構建了<1 nm的晶體管。通過化學氣相沉積大面積的石墨烯和MoS2,在2英寸晶圓上構建晶體管器件,器件的開關比達到1.02×105,閾下擺幅值低于117 mV dec-1,模擬結果顯示MoS2晶體管在打開狀態的有效尺寸僅僅0.34 nm,關閉狀態尺寸為4.54 nm。這項工作為Moore定律突破晶體管的尺度下限提供機會,有助于發展下一代電子學器件。

圖1. 亞1納米柵長晶體管結構示意圖

研究背景

自從1960年代人們首次在晶硅上搭建大規模集成電路,硅基晶體管的發展一直都遵循著Moore定律規則,逐步降低晶體管的尺寸,能夠在芯片上構建更多數量的晶體管。目前,硅基晶體管的大小接近了理論所能達到的極限,硅晶體管的尺寸已經小于5 nm,理論分析結果認為進一步縮小器件的大小面臨短溝道效應SCE(short channel effects),導致源極-柵極隧穿電流、漏致勢壘降低DIBL(drain-induced barrier lowering),因此無法進一步降低硅晶體管的尺寸。

目前基于V形槽濕法刻蝕技術得到的最好Si晶體管尺寸為3 nm,因此需要尋找新型材料能夠突破目前尺寸規律的限制。

二維材料的機會

圖2. 0.34 nm尺寸單層MoS2晶體管器件結構和表征 (a-f) 晶體管制備方法 (a) 化學氣相沉積石墨烯薄膜 (b) 沉積Al層 (c) Al層自動氧化 (d) SiO2刻蝕 (e) 原子層沉積HfO2 (f) 化學氣相沉積石墨烯轉移、圖案化、沉積金屬電極 (g) 單層MoS2構建的0.34 nm晶體管示意圖 (h) SEM著色圖 (i) 晶體管器件的TEM圖 (j) 元素分布EDS圖 (k) 在2英寸晶圓上搭建的晶體管光學圖。

近些年間二維材料受到廣泛關注,被認為有可能成為下一代電子學器件的主要材料。石墨烯作為一種半金屬材料具有較高的導電性,能夠作為電極材料,MoS2作為一種代表性的二維過渡金屬硫化物半導體,具有比Si(1.18 eV)更高的能帶寬度(2.0 eV);MoS2作為一種n型半導體,具有更大的有效質量、更低的介電常數,因此能夠避免產生SCE效應。MoS2材料由于具有以上的優異性能,被認為是替換Si用于未來晶體管的材料。

新發展

作者制備了垂直MoS2晶體管器件,其中使用小于1 nm的石墨烯作為晶體管柵極,通過大面積氣相沉積的石墨烯和MoS2實現晶圓尺寸大規模晶體管集成。使用鋁屏蔽頂部石墨烯產生的垂直電場,因此有效電場來自石墨烯的邊緣,這種電場只能夠影響垂直MoS2溝道中的一部分。化學氣相沉積得到的石墨烯薄膜具有優異的導電性,能夠有效的阻礙電壓衰減。

尺寸為0.34 nm的垂直晶體管具有優異的開關比(1.02×105)。計算模擬結果顯示石墨烯的2D平面結構有助于實現柵極作用,能夠耗盡與石墨烯平面相連的垂直MoS2側壁溝道。

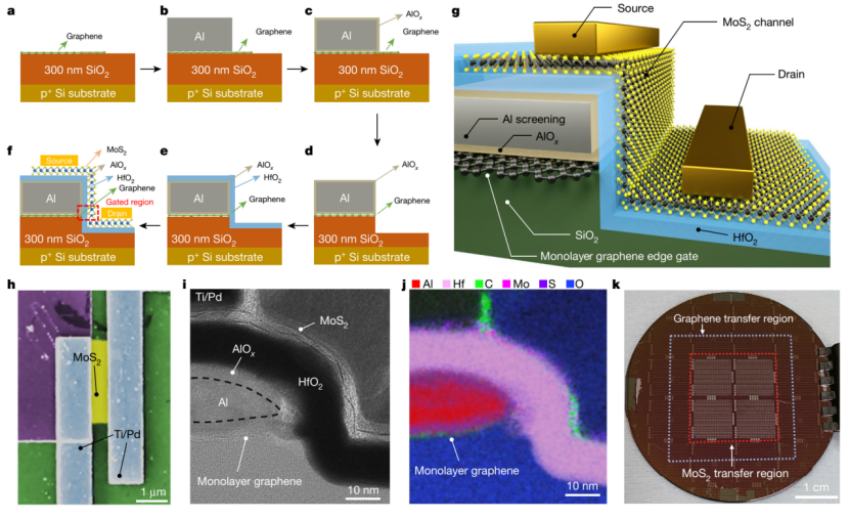

這項工作為發展低于1 nm的晶圓量級晶體管提供機會,更加重要的一點在于,這項工作是迄今為止相關報道中柵極長度最小的晶體管。

意義

圖3. 近些年晶體管尺寸的發展。

在各種晶體管中,電流從源極流動到漏極,該過程通過柵極控制電流,通過施加不同電壓實現控制柵極的打開和關閉,因此柵極的大小對于晶體管的尺寸至關重要。

二維材料在新型電子學材料可能至關重要,2016年,斯坦福大學報道通過金屬態碳納米管和MoS2構建了1 nm大小的柵極。清華大學這項工作實現了進一步突破性發展,通過單層石墨烯與MoS2構建了0.34 nm(對應于單層石墨烯的原子層厚度)的柵極。未來能夠比這項工作更小的晶體管基本上無法實現,因此這項工作可能意味著到達摩爾定律的終點線。

論文通訊作者為清華大學集成電路學院任天令教授和田禾副教授,清華大學集成電路學院2018級博士生吳凡、田禾副教授、2019級博士生沈陽為共同第一作者,其他參加研究的作者包括清華大學集成電路學院2020級碩士生侯展、2018級碩士生任杰、2022級博士生茍廣洋、楊軼副教授和華東師范大學通信與電子工程學院孫亞賓副教授。

參考文獻

Wu, F., Tian, H., Shen, Y. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022)

DOI: 10.1038/s41586-021-04323-3

https://www.nature.com/articles/s41586-021-04323-3