10月27日,《Nature Electronics》報道了一項基于 2D/3D InSe/Si 的異質隧道三極管的研究。此項研究由賓夕法尼亞大學、中科院上海技術物理研究所、美國國家標準與技術研究院和美國空軍研究實驗室合作開展。

研究背景

功耗是現代高度規模化納米電子的核心問題。單帶傳輸的熱離子器件由于亞閾值斜率(SS,Subthreshold Slope)的基本限制,例如在金屬氧化物半導體場效應晶體管 (MOSFET)中,其在功耗和電源電壓的進一步縮放受到阻礙,并且基于MOSFET 電路中功率密度和耗散也會增加。理想MOSFET在室溫下的 SS 限制為 ,其中kB是玻爾茲曼常數,q是基元電荷,T是溫度。這是由于金屬-半導體接觸處載流子注入的熱特性,這對每個開關周期的功耗設置了下限。隧道場效應晶體管(TFET,Tunnel Field-Effect Transistors)可以潛在地克服這一限制,因為其工作原理是基于帶隙隧穿(BTBT,Band-To-Band Tunneling)而不是熱離子發射。然而,TFET 在低于 60?mV?decade?1 運行時具有低導通電流密度和低開/關比的問題。

2D半導體為 TFET 器件設計提供了新的機遇,它們的原子級厚度使得強靜電控制成為可能。這種靜電控制降低了 TFET 的 SS,并可以通過最大化導通電流密度得以提高開/關比。此外,二維范德華材料表面沒有懸鍵,因此它們很容易地嵌入金屬柵極和薄電介質之間,實現強靜電調制。但是,與具有完善摻雜方案的 3D材料不同, 2D 材料中穩定和互補摻雜的問題仍然難以克服。因此,結合 2D與 3D 半導體是一種發展TFET 架構潛在且有價值的方法。

主要研究內容

研究者們制作了基于由 n 型 2D InSe 和 p 型重摻雜 (p++) 的3D Si 形成的范德華異質結構的柵極可調異質隧道三極管(HJ-TT,Heterojunction Tunnel Triodes)。該器件克服了傳統 MOSFET 的熱離子限制,在四個數量級的漏極電流內提供 6.4? mV? decade?1 的最小 SS 和 34 ?mV? decade?1 的平均 SS 。它們還表現出 Ip-Si?=?0.3 ?μA? μm–1 的大導通電流密度(漏極偏壓為 Vp-Si?=??1?V時)。

器件制作和構筑

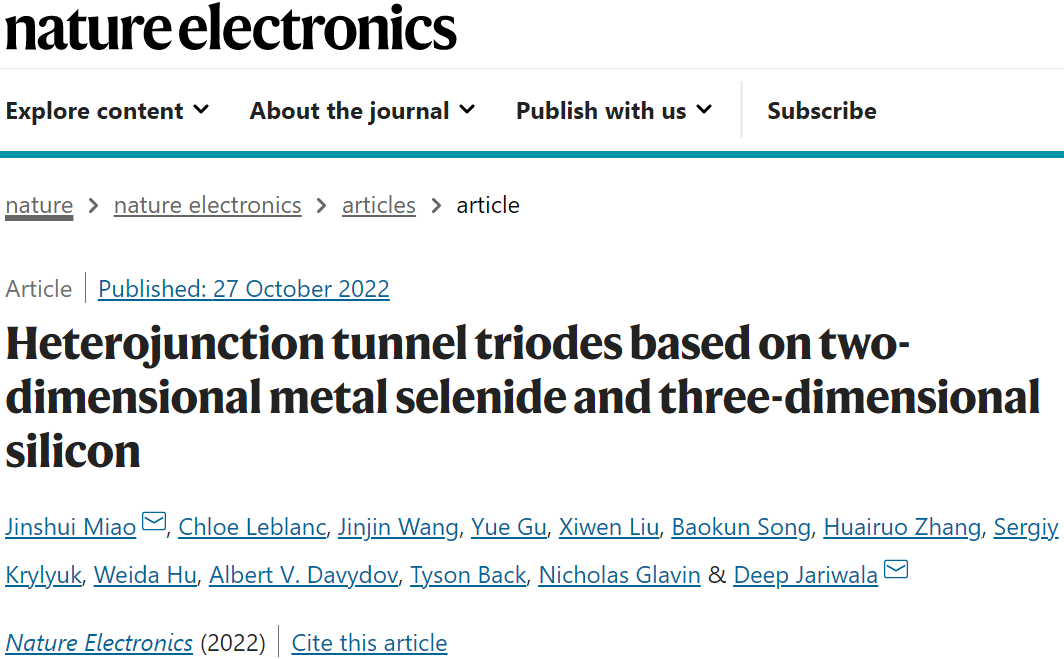

首先,在 SiO2/p++Si 襯底表面蝕刻方形窗口,以暴露下部 p++Si 層。然后,將機械剝離的數層厚度的 2D InSe 薄片轉移到暴露的表面上(圖 1)。InSe 和 p++Si之間的超薄非晶 SiOx具有高導電性,器件的橫向電阻僅為 ~25 ?Ω。并且,這些氧化硅可以通過氫氣處理還原。

圖1 2D/3D 隧道三極管的結構和表征。(a)n-InSe/p++Si 2D/3D HJ-TT 的示意圖,其中 3D p++Si、2D n-InSe、AlOx 柵極電介質和 Ti/Au 金屬電極垂直堆疊在一起;(b)2D/3D HJ-TT 和頂柵n-InSe MOSFET 的光學顯微照片,比例尺為10? μm;(c)n-InSe/p++Si HJ-TT橫截面結構的明場 STEM 圖像,比例尺為10 ?nm;(d)二維 InSe 的層狀晶體結構,比例尺為5 nm;(e)介于 2D InSe 和單晶 3D p++Si 之間的 2nm 厚的非晶原生 SiOx,比例尺為2 nm;(f)原子分辨率的 HAADF-STEM 圖像與投影原子模型,比例尺為1 nm。

器件性能

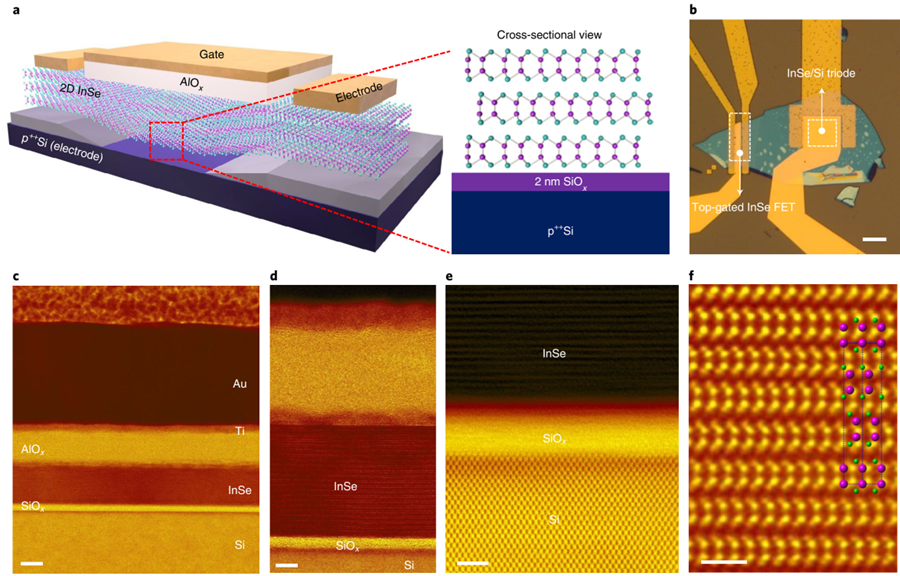

該器件在最小 SS 值(6.4? mV? decade–1)的電流開/關比為 106,并在 Vp-Si?= ?1?V時具有 Ip-Si? =? 0.3? μA?μm–1的通態電流密度(圖 2a)。將圖 2a中 ?6.00 V到?5.82 ?V的傳輸特性放大(Vp-Si?= ?1?V),如圖 2b所示,可以發現僅僅 180?mV 的柵極電壓變化將輸出電流調制超過五個數量級。此外,與漏極電流相比,柵極漏電流的大小可以忽略不計。因此,Igate僅會引起關態電流非常小的波動,并對亞閾值或閾值以上區域的信號幾乎沒有影響。圖 2c 表明六個 InSe/Si 器件的SS 均低于 60? mV? decade–1。為了進一步說明 2D/3D HJ-TT 中的載流子傳輸,研究者們進行了 Sentaurus計算機輔助設計技術(TCAD,Technology Computer-Aided Design)模擬。模擬的 Ip-Si-VG 特性曲線與實驗結果相近,平均 SS 小于 10? mV? decade–1,電流開/關比高達 109(圖 2d,e)。如圖 2f 顯示了TCAD 模擬的電場輪廓和電子密度圖。

圖2 InSe/Si 2D/3D HJTT 的室溫電學特性。(a)InSe/p++Si HJ-TTs 在室溫下的Ip-Si-VG 傳輸特性,Vp-Si?=??0.5?V(黑色)和 Vp-Si?=??1.0?V(紅色)圖(綠線表示的柵極漏電流);(b) Vp-Si?=?–1?V 時(a)VG從 ?6.00 V到?5.82 ?V的傳輸特性;(c) SS 與六個代表性 InSe/Si HJ-TT 器件的輸出電流 Ip-Si 的關系;(d)TCAD 模擬預測的 InSe/Si HJ-TT 傳輸特性;(e)TCAD 模擬 InSe/Si HJ-TT 的 SS 與輸出電流 Ip-Si;(f)TCAD 模擬的跨 InSe/Si HJ-TTs 在開 (i) 和關 (iii) 狀態下的電場輪廓,模擬 InSe/Si HJTT 在開 (ii) 和關 (iv) 狀態下的電子密度分布,比例尺為2.5 ?nm。

電荷傳輸機制

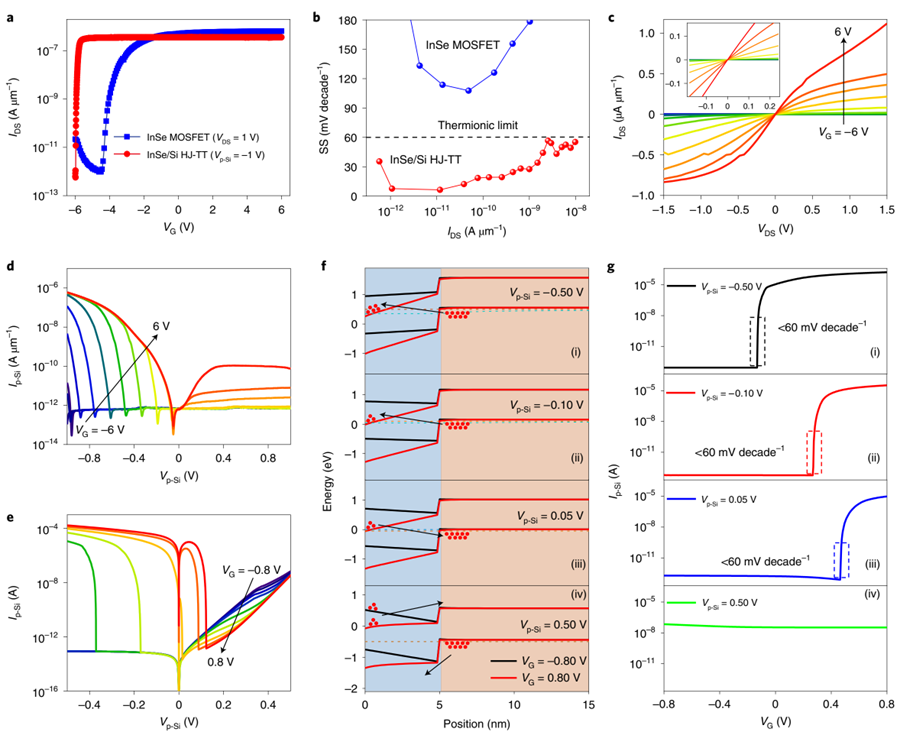

根據平衡能帶圖和電子親和能(2D InSe,4.60?eV;3D Si,4.01?eV)以及載流子濃度,InSe/Si 形成具有 0.59?eV 價帶偏移的 II 型異質結。為了進一步評估 InSe/Si HJ-TT 的電學特性,研究者對圖 1b 中在同一 InSe 晶體上制造的控制 MOSFET 和 InSe/Si HJ-TT 進行比較。在控制 InSe MOSFET 和 InSe/Si 2D/3D HJ-TTs 器件之間有三個明顯的差異:一、InSe MOSFET 的電流密度高于 InSe/Si HJ-TTs;二、對于相同的氧化層厚度,InSe MOSFET的平均 SS 要高三倍以上(圖 3a,b);三、 InSe MOSFET 具有線性輸出特性,而 InSe/Si HJ-TT具有柵極可調整流比的整流輸出(圖 3c,d)。這些差異進一步表明InSe/Si HJ-TT 確實具有不同的電荷傳輸機制,即 BTBT。為了進一步了解 InSe/Si HJ-TT 中的整流 Ip-Si-Vp-Si特性,Sentaurus TCAD 再次用于系統地研究輸出特性(圖 3e)、能帶圖(圖 3f)和 相應的傳輸特性(圖 3g)。

圖3 InSe/Si 2D/3D HJTT、控制 2D InSe MOSFET 和 TCAD 模擬器件的室溫電學特性。(a)InSe MOSFET 和InSe/Si HJ-TT 的IDS-VG 傳輸特性的比較;(b)InSe/Si HJ-TT 與控制InSe MOSFET亞閾值斜率的比較;(c)控制 InSe MOSFET 的線性 IDS-VDS 輸出特性;(d)InSe/Si HJ-TT 的Ip-Si-Vp-Si的對數輸出特性;(e)TCAD 模擬的 InSe/Si HJ-TT 的 Ip-Si-Vp-Si輸出特性;(f,g)TCAD 模擬的 InSe/Si 能帶結構和各種 Vp-Si 和 VG 值對應的 Ip-Si-VG 轉移特性曲線。

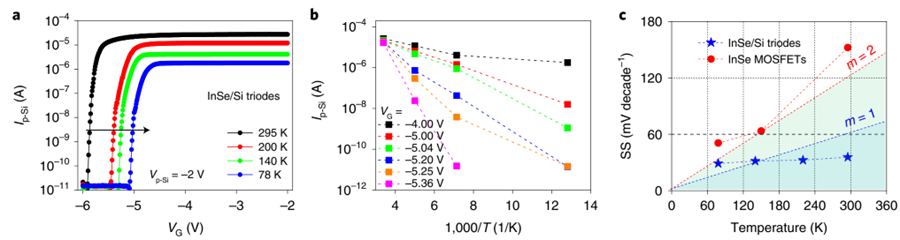

為了進一步證明 InSe MOSFET 和 InSe/Si HJ-TT 的電荷傳輸機制之間的差異,研究者們進行了與溫度相關的電學表征(圖 4)。BTBT 的閾值電壓似乎隨著溫度的降低而明顯向右移動(圖 4a)。此外,痛態電流平臺的幅度也隨著溫度的降低而降低。這表明器件的傳輸機制是復雜的,并且隨著柵極電壓/二維 InSe 中費米能級的位置而變化。從 Arrhenius 曲線(圖 4b)中可以看出,亞閾值區域的激活能為 0.2? eV。此外,隨著柵極電壓從 ?5.36 變為 ?4.00 ?V,該活化能從 0.20 變為 0.05 ?eV,這表明對于高摻雜密度(VG ?=? ?4.00 ?V),傳輸對溫度的依賴性很小。眾所周知,對于傳統 MOSFET 中的熱離子傳輸, SS 線性地取決于溫度。然而,如圖 4c所示,研究者發現InSe/Si HJ-TT的SS幾乎與溫度無關,并與 InSe MOSFET 形成鮮明對比。這有力表明 BTBT 機制主導了在 InSe/Si HJ-TT 陡峭的SS 范圍內的傳輸。

圖4 InSe/Si 2D/3D HJ-TTs 的溫度相關電學特性。(a)溫度相關的 Ip-Si-VG 傳輸特性;(b)不同柵極電壓下漏極電流與 1,000/T的 Arrhenius 曲線;(c)InSe/Si 2D/3D HJ-TT 和 InSe 控制 MOSFET 的亞閾值擺幅隨溫度的變化曲線。

性能比較

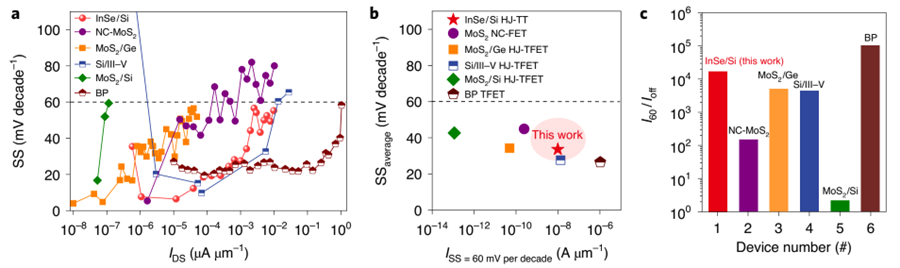

研究者們將本研究中制作的器件與已報道的器件進行了性能比較,聚焦于三個重要指標:一、SS 與漏極電流密度的關系;二、SS? =? 60? mV ?decade–1 時漏極電流與平均 SS 的關系;三、 SS ?= ?60?mV? decade–1 時的電流與低于 60 ?mV? decade–1 區域時關態電流的關系。圖 5a清楚地表明, InSe/Si HJ-TTs 具有小 SS和高 I60(SS ?=?60?mV? decade–1 時),并且電流密度比 MoS2/Ge TFET 大兩個數量級以上。盡管一些同質結和異質結器件顯示出稍優的 SS 平均值(圖 5b)或 I60/Ioff(圖 5c),但 InSe/Si 異質結構在與硅技術集成和合適帶隙的全固態器件方面仍然表現出顯著優勢。

圖5 InSe/Si 2D/3D HJ-TT 與報道的亞熱離子同質結和異質結 TFET 以及 NC-FET 的性能比較。(a)各種亞熱離子 FET 的亞閾值擺幅與漏極電流的函數關系;(b)平均 SS 與漏極電流的關系;(c)各種亞熱離子器件的I60/Ioff。

結論

研究者們報道了基于2D/3D InSe/Si的 BTBT HJ-TT。由于 2D InSe 的原子級厚度和 3D Si 中的固定摻雜分布,能帶可以通過電容耦合柵極有效調制,從而實現能帶強調制對齊,進而產生直接 BTBT。由此產生的 HJ-TT 在室溫下四個數量級漏極電流范圍內表現出 6.4?mV?decade–1 的最小 SS 和34.0?mV?decade–1 平均 SS。在 Vp-Si? =? ?1 ?V 時,這些器件還具有高達 106 的高電流開/關比和 0.3 ?μA?μm–1的通態電流密度。結果表明,2D/3D 集成是實現超低功耗和高度集成邏輯開關的有效途徑。

參考文獻:

Heterojunction tunnel triodes based on two-dimensional metal selenide and three-dimensional silicon, Nature Electronics (2022).