特別說明:本文由學研匯技術 中心原創撰寫���,旨在分享相關科研知識。因學識有限,難免有所疏漏和錯誤�����,請讀者批判性閱讀�,也懇請大方之家批評指正。研究背景

芯片為大數據和人工智能的發展提供源源不斷的動力,芯片速度的提升得益于晶體管的微縮�,然而當前傳統硅基場效應晶體管的性能逐漸接近其本征物理極限��。國際半導體器件與系統路線圖(The International Roadmap for Devices and Systems, IRDS)預測硅基晶體管的極限柵長將停止在12 nm,工作電壓不能小于0.6 V,這定義了未來硅基芯片縮放過程結束時的最終集成度和功耗���,因此亟需發展新型溝道材料來延續摩爾定律��。

關鍵問題

原子級厚度的二維半導體因其超薄體和高遷移率的優勢�,是極具潛力的芯片溝道材料�����,全球多家領先半導體制造公司與研究機構均對其投入大量研究�。但2D半導體和高k介質之間的低質量界面�����,2D半導體-金屬界面上具有相當大肖特基勢壘的源極和漏極接觸�����,以及2D半導體固有的缺點限制了其發展。迄今為止所有二維晶體管所實現的性能均不能媲美業界先進硅基晶體管����,其實驗結果遠落后于理論預測�����,不足以展示二維半導體的最終潛力。

新思路

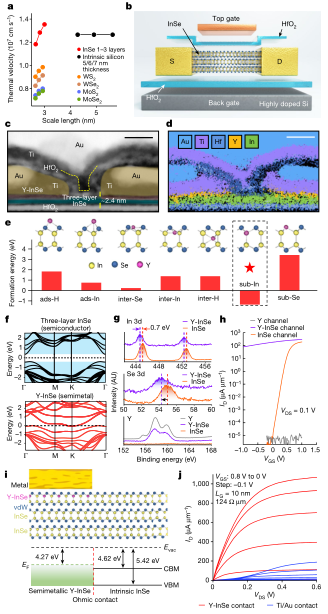

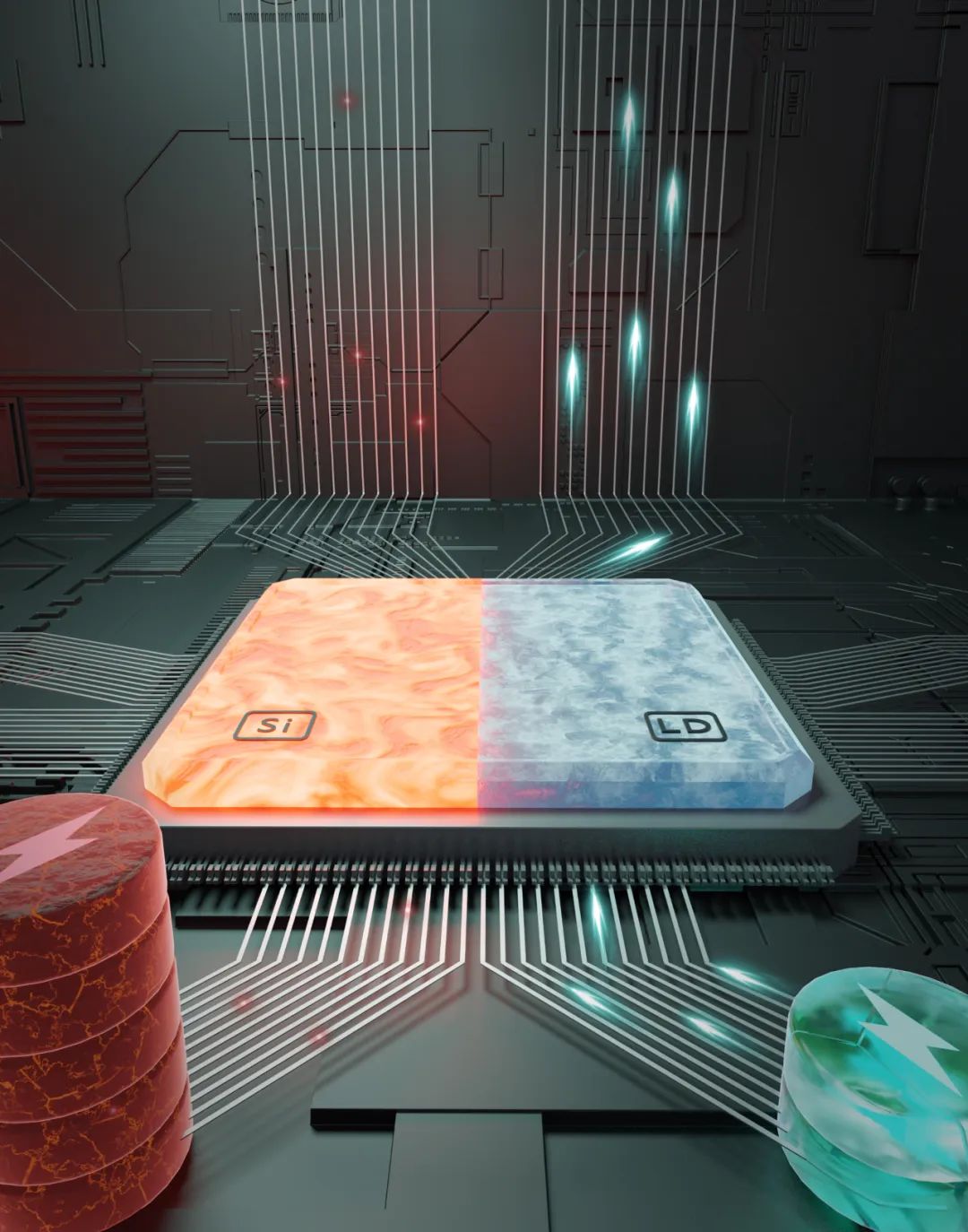

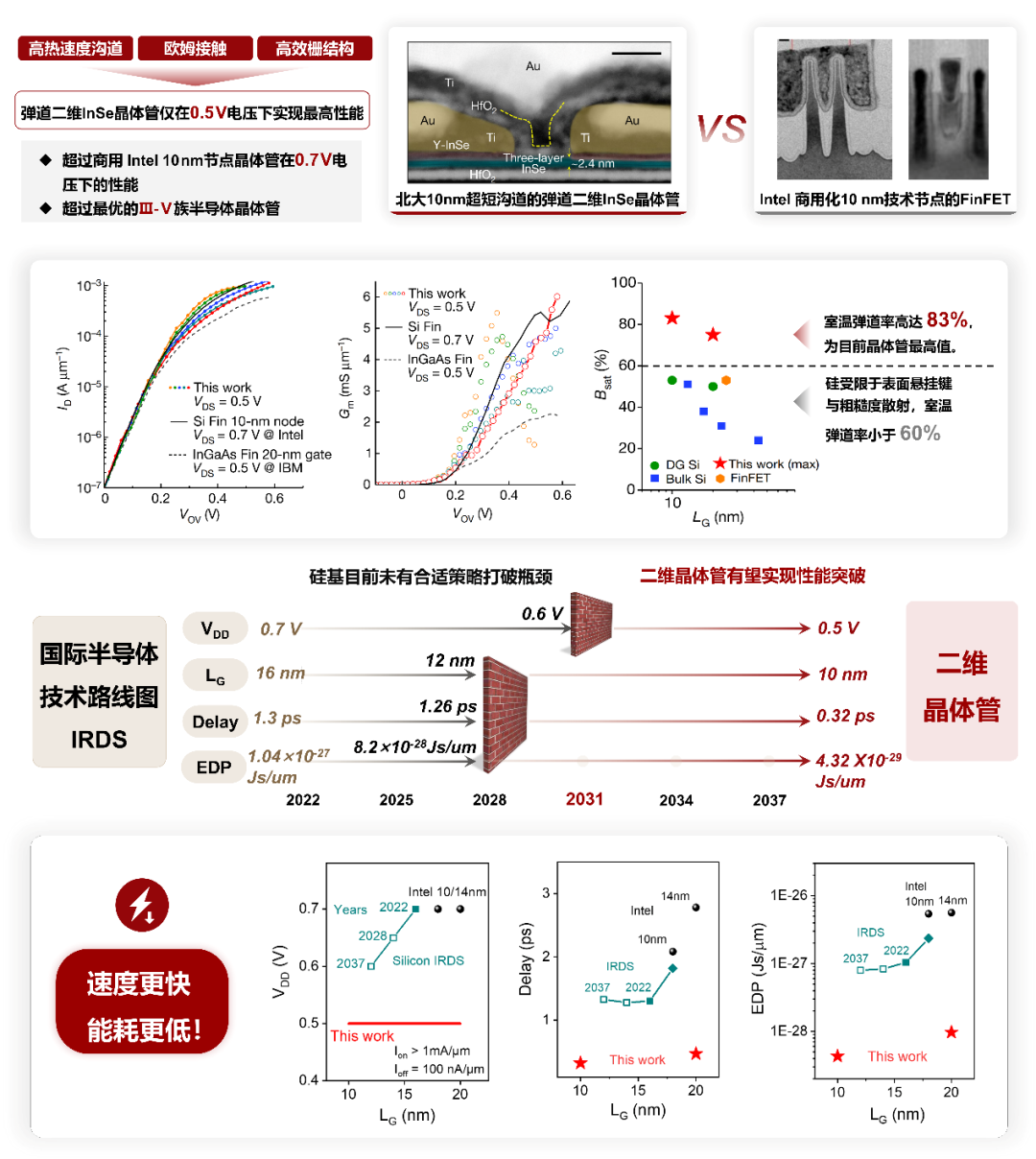

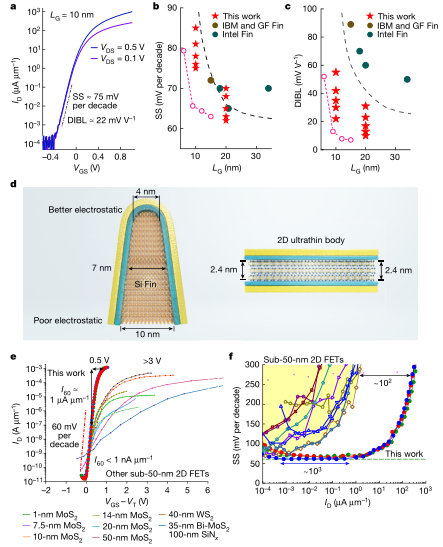

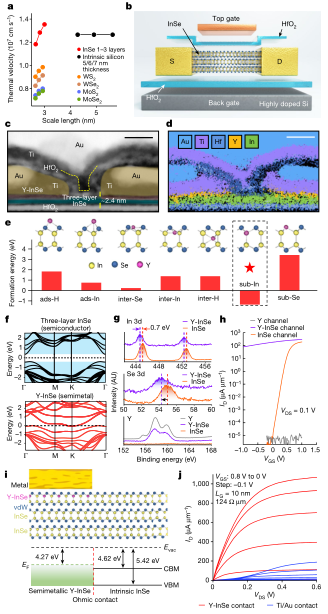

有鑒于此�,北京大學電子學院彭練矛教授-邱晨光研究員課題組等人報道了一種以2D硒化銦(InSe)為溝道材料的高熱速場效應晶體管�,在0.5 V下工作��,實現了6 mS μm?1的高跨導和飽和區83%的室溫彈道比�����,超過了任何已報道的硅基場效應晶體管。作者提出了一種摻雜釔誘導的相變方法來實現銦硒場效應晶體管的歐姆接觸�,同時將硒化銦場效應晶體管的溝道長度縮小到10 nm����。該InSe FETs可以有效抑制短通道效應��,其低亞閾值擺動(SS)為75 毫伏量程,漏極誘導的勢壘降低(DIBL)為22 mV V?1�����。此外����,在10 nm彈道InSe FETs中可靠地提取了62 Ω μm的低接觸電阻,導致了更小的內在延遲和更低的能量延遲積(EDP)�����,遠低于預測的硅極限�����,將n型二維半導體晶體管的性能首次推近理論極限��。

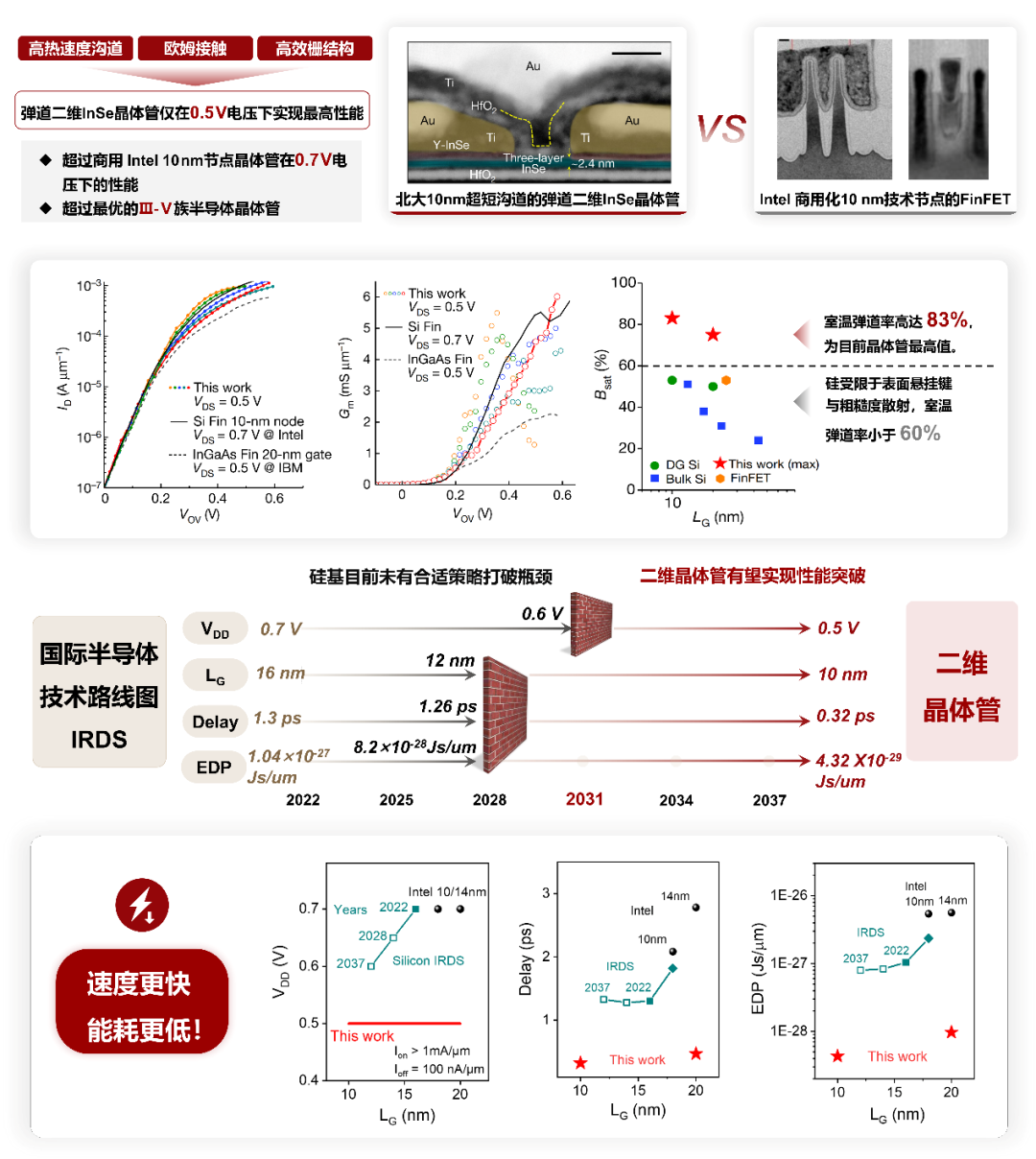

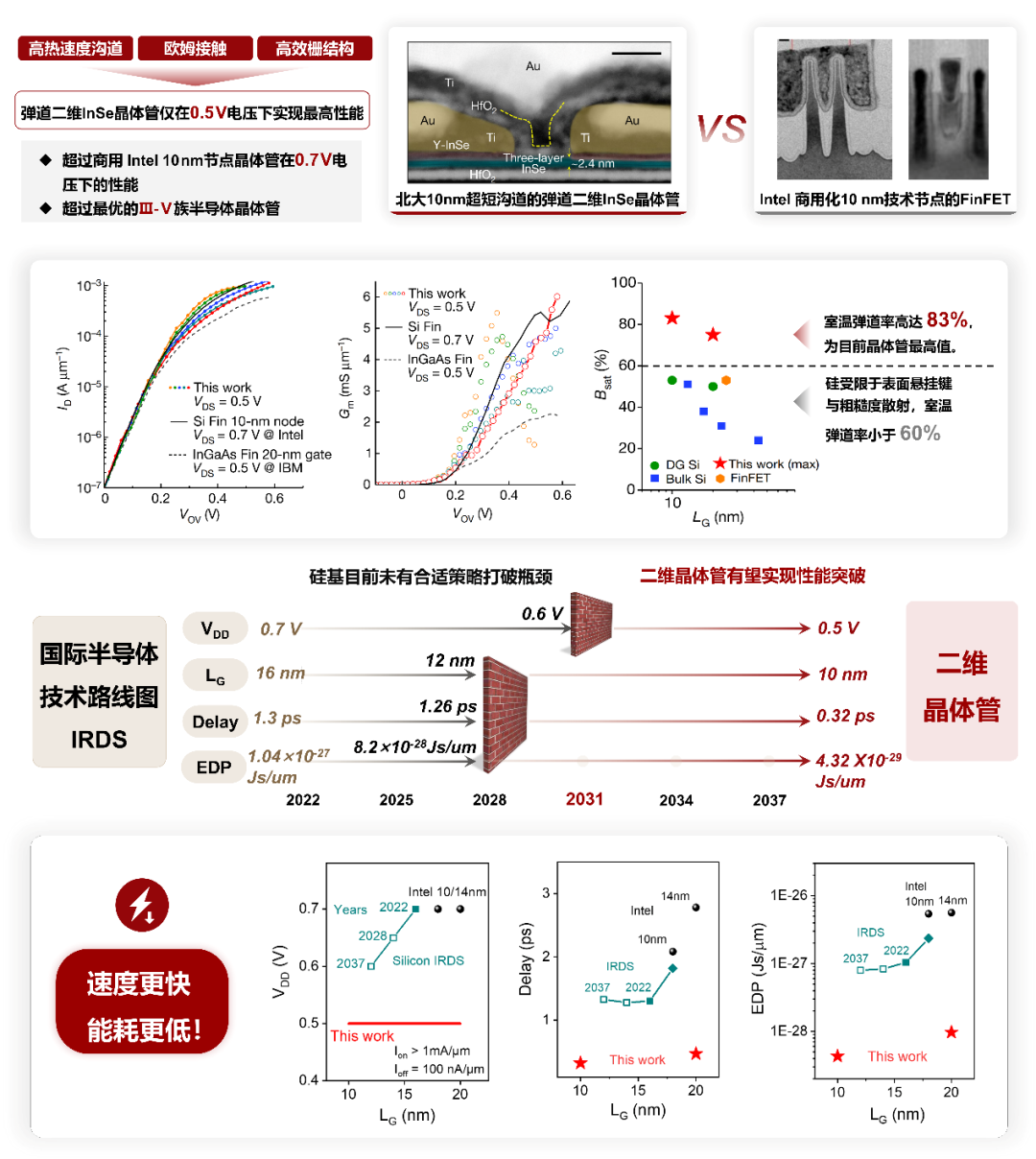

作者構建了三層InSe構建超短彈道晶體管�����,展示了2D InSe晶體管結構的示意圖��,并通過釔摻雜將半導體InSe轉化為半金屬Y-InSe以克服金屬電極與二維半導體之間的大接觸電阻����。作者表明了2D InSe FETs具有高注入速度和優異的歐姆接觸���,證實了彈道晶體管中實現了歐姆接觸���,并計算了InSe彈道晶體管接觸電阻的量子極限���。3���、通過與硅基FETs轉移特性比較�����,證實了2D InSe FETs的優越將2D InSe FETs與硅FETs的性能進行比較��,證實了2D InSe FETs在飽和電流、導通電流��、彈道比����、延遲和EDPs等方面的優異性。4、比較了InSe FETs與硅Fin FETs的短通道效應作者比較了InSe FETs與硅fin FETs的短通道效應,結果表明10納米FETs表現出更好的SS和DIBL��。進一步研究結果表明�����,雙柵結構在抑制短通道效應方面比單柵結構有效得多�����。1、實現的二維半導體晶體管性能首次超越Intel商用10 納米節點硅基Fin晶體管作者制備了10納米超短溝道彈道二維硒化銦晶體管�����,采用高載流子熱速度(更小有效質量)的三層硒化銦作溝道�����,實現了6 mS μm?1的高跨導和飽和區83%的室溫彈道比,首次使得二維晶體管實際性能超過硅基Fin晶體管。將二維晶體管的工作電壓降到0.5 V,這也是世界上迄今速度最快能耗最低的二維半導體晶體管�。3����、解決了二維材料表面生長超薄氧化層的瓶頸問題本工作解決了二維材料表面生長超薄氧化層的難題�,制備出2.6納米超薄雙柵氧化鉿,將器件跨導提升到6 毫西?微米��,超過所有二維器件一個數量級���。作者開創了摻雜誘導二維相變技術,將總電阻刷新至124歐姆?微米�����,滿足集成電路未來節點對晶體管電阻的要求(220歐姆?微米)���。溝長縮小到10 nm(超越硅基極限12nm)�����;電壓縮小到0.5V (超越2031年硅基極限0.6V);門延時縮減到0.32 ps, 四倍優于硅基極限1.26ps�����;功耗延遲積縮減到4.32×10-29焦秒/微米�����,比硅基極限低一個量級�。

技術細節

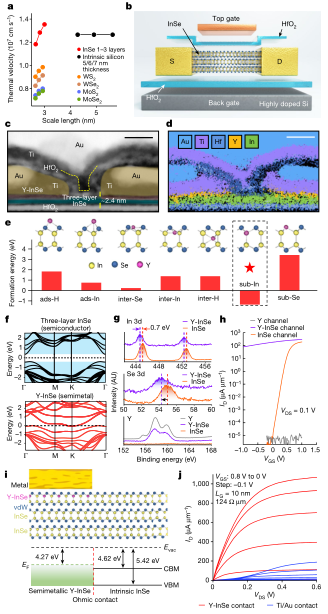

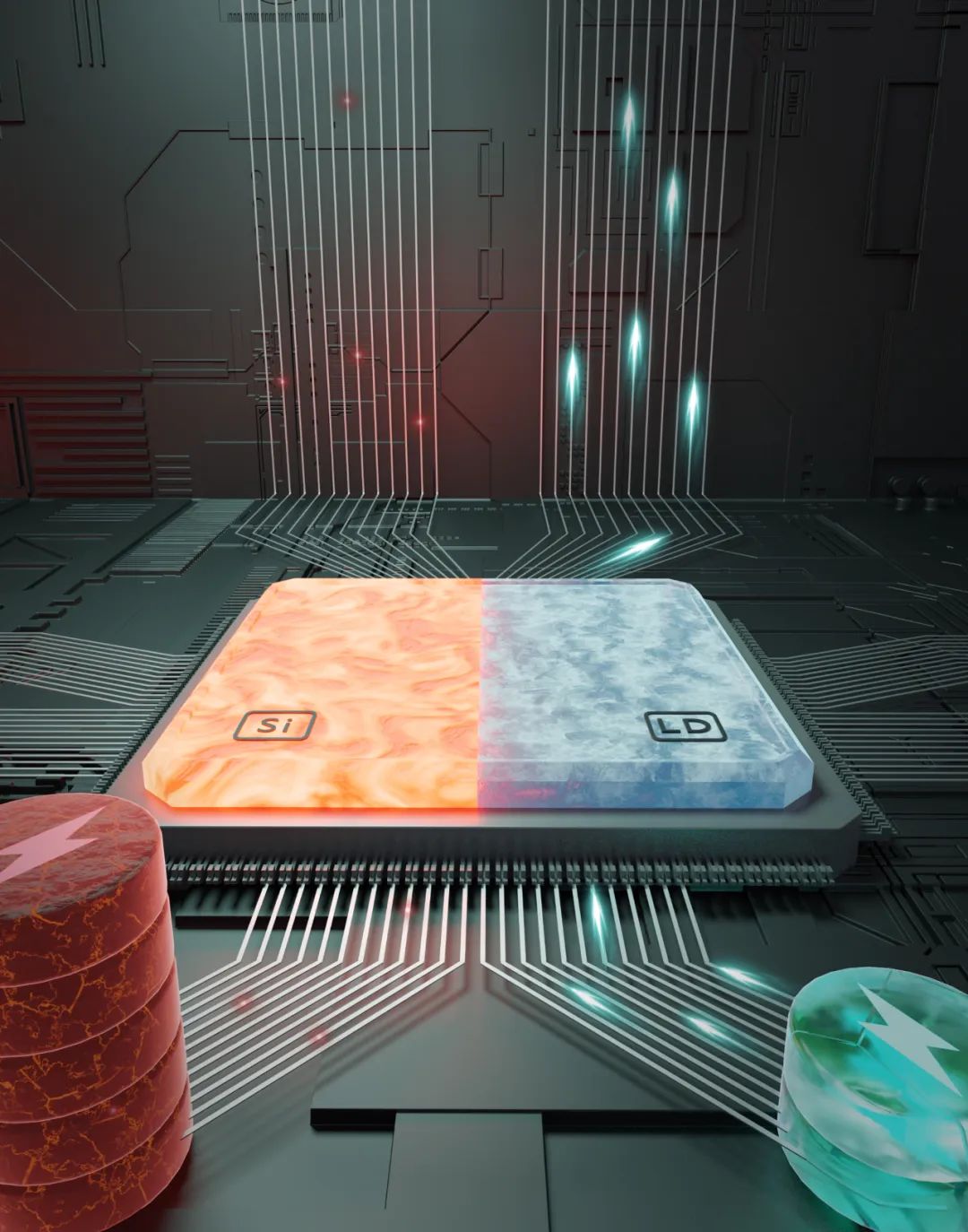

通過參考熱速度和自然長度兩個關鍵參數設計具有良好開關特性的超尺度彈道晶體管的基本物理規則��。作者使用三層InSe構建超短彈道晶體管�,旨在探索2D半導體的終極潛力����。作者展示了2D InSe晶體管結構的示意圖,確認了二維InSe通道���、HfO2介質、電極的位置����,以及一層薄薄的釔的存在�����。為了克服金屬電極與二維半導體之間的大接觸電阻,作者在接觸區采用了一種相變方法�,利用釔摻雜將半導體InSe轉化為半金屬Y-InSe�����。電傳遞特性有力地證明了摻雜Y-InSe為通道的場效應晶體管具有半金屬性質,柵場調制特別弱(開/關比<10)����。使用半金屬Y-InSe觸點的典型InSe場效應管的總電阻為124 Ω μm,比使用傳統Ti/Au觸點的總電阻小兩個數量級���,從而在輸出特性方面具有優越的導態性能。

圖 彈道InSe FETs的結構和電子特性(圖片來源:Nature)與其他報道的2D短通道FETs相比����,本工作報道的2D InSe FETs具有高注入速度和優異的歐姆接觸���,僅需要0.4 V的漏極電壓(VDS)就可以使電流飽和并超過1 mA μm?1���。歐姆接觸彈道10納米2D InSe FETs在寬溫度范圍內(300 K至100 K)具有恒定的開態電流���,證實了彈道晶體管中實現了歐姆接觸����。在長通道擴散FETs中���,隨著溫度的升高����,溝道內的散射增加,導致開態電流減小����, InSe FETs的閾下轉移特性中只存在一個單一的熱發射區(缺乏熱場發射區)����,證明了在InSe FETs中實現肖特基勢壘可忽略的歐姆接觸�。此外,用郎道爾公式計算了InSe彈道晶體管接觸電阻的量子極限����。

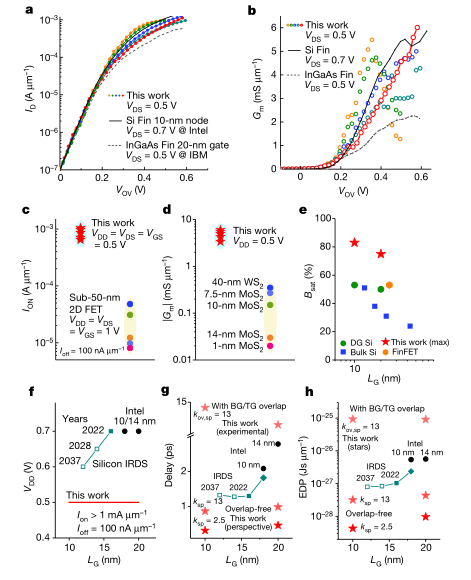

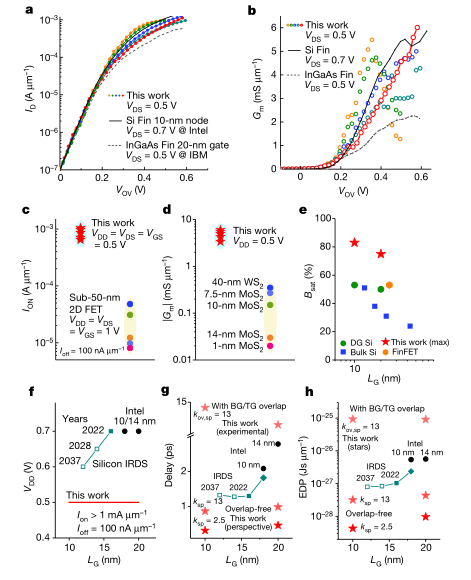

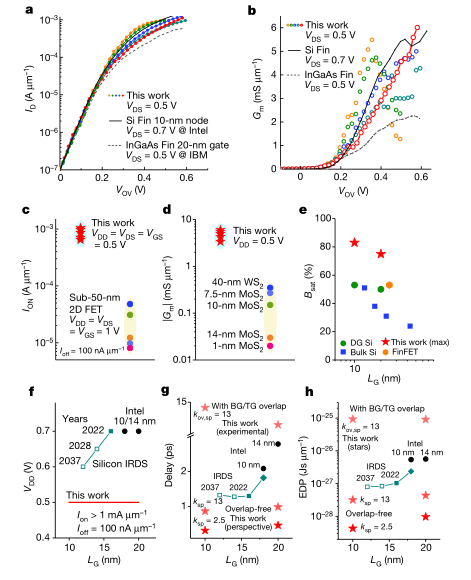

圖 InSe FETs的電子特性及總電阻(圖片來源:Nature)為了將2D InSe FETs的性能與硅FETs的性能進行基準測試,直接2D InSe FETs的典型傳輸特性與10納米節點硅(英特爾)和20納米門InGaAs (IBM) fin FETs的傳輸特性進行比較。具體優勢如下:(1). 2D InSe FETs的飽和電流與硅FinFET相當��,超過了InGaAs FinFET��。在2D InSe FETs中實現了6 mS μm?1 (0.5 V)的記錄峰值跨導��,這是所有報道的低維納米材料FETs的最高值,與Si 10納米節點FinFET(英特爾)相當���,但電壓較低0.5 V(硅為0.7 V)�����,比InGaAs FinFET (IBM)大三倍。(2). 在VDD=0.5 V的超低電壓下,2D InSe FETs導通電流范圍為0.7~1.2 mA μm?1,跨導范圍為3 ~ 6ms μm?1�����,比其他2D FETs大大約一個數量級��。(3). 2D FETs飽和區域的室溫彈道比被提取出來��,達到了83%以上,這是迄今為止所有2D晶體管的最高記錄值�,超過了之前報道的所有硅FETs�����。(4). InSe FETs的VDD被縮小到0.5 V,仍能夠切換通道�,電流從100 nA μm?1(關閉狀態)到超過1 mA μm?1(打開狀態)�����,這對于Si single-sheet MOS FET是不可能的。(5). InSe FETs在延遲和EDPs(無重疊結構)方面比硅fet表現出更好的縮放趨勢。最佳10nm柵長InSe場效應晶體管的延遲為0.32 ps和0.87 ps��,這比IRDS 2022預測的Si場效應晶體管的最終延遲要好�����。(6). 10 nm柵長InSe FETs的EDPs低至4.32 × 10?29 Js μm?1和3.20 × 10?28 Js μm?1,遠小于Si FETs的預測極限���。

圖 對標InSe,硅和InGaAs FETs(圖片來源:Nature)

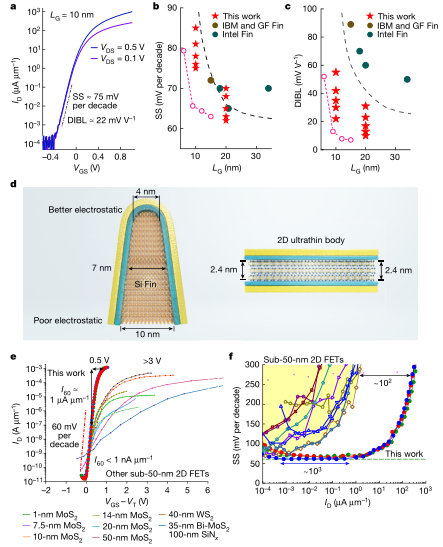

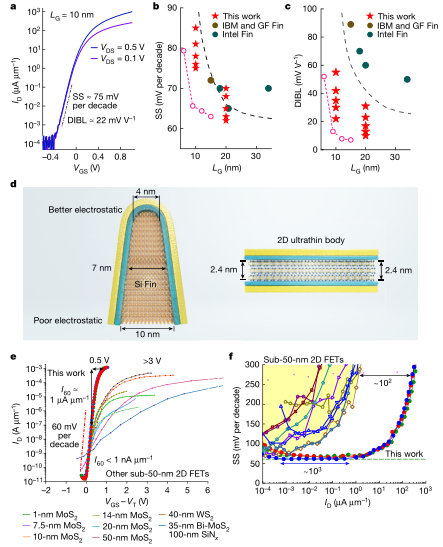

圖 彈道二維硒化銦晶體管與先進節點硅基晶體管的比較(圖片來源:北京大學)10納米InSe FET的典型傳輸特性顯示了理想的開關行為�,包括75 毫伏量程的SS, 22 mV V?1的DIBL和超過7個數量級的電流開/關比���。10nm InSe場效應晶體管的離態泄漏電流小于1nA μm?1���,滿足商用標準性能IC的要求�。將InSe FETs的SS和DIBL的標度趨勢與最先進的硅FETs的理論模擬進行了比較���。結果表明10納米FETs表現出更好的SS和DIBL�。均勻厚度為2.4 nm的三層2D InSe通道表現出遠低于50 mV V?1的DIBL。模擬預測,通過將2D溝道從三層細化為單層����,10nm柵長2D FETs的SS可以進一步降低到65 毫伏量程, DIBL可以進一步降低到17mV V?1���,為進一步優化off-state泄漏電流提供了足夠的空間�。進一步研究結果表明���,雙柵結構在抑制短通道效應方面比單柵結構有效得多�����。與其他報道的2D FETs相比��,該彈道InSe FETs在更大的電流量級下具有更陡的SS。歐姆接觸的實現不僅有助于大的導通電流和大的跨導��,而且是在近閾值區域實現理想開關特性的一個容易被忽視的先決條件�����。

圖 InSe FETs與硅fin FETs的短溝道效應比較(圖片來源:Nature)

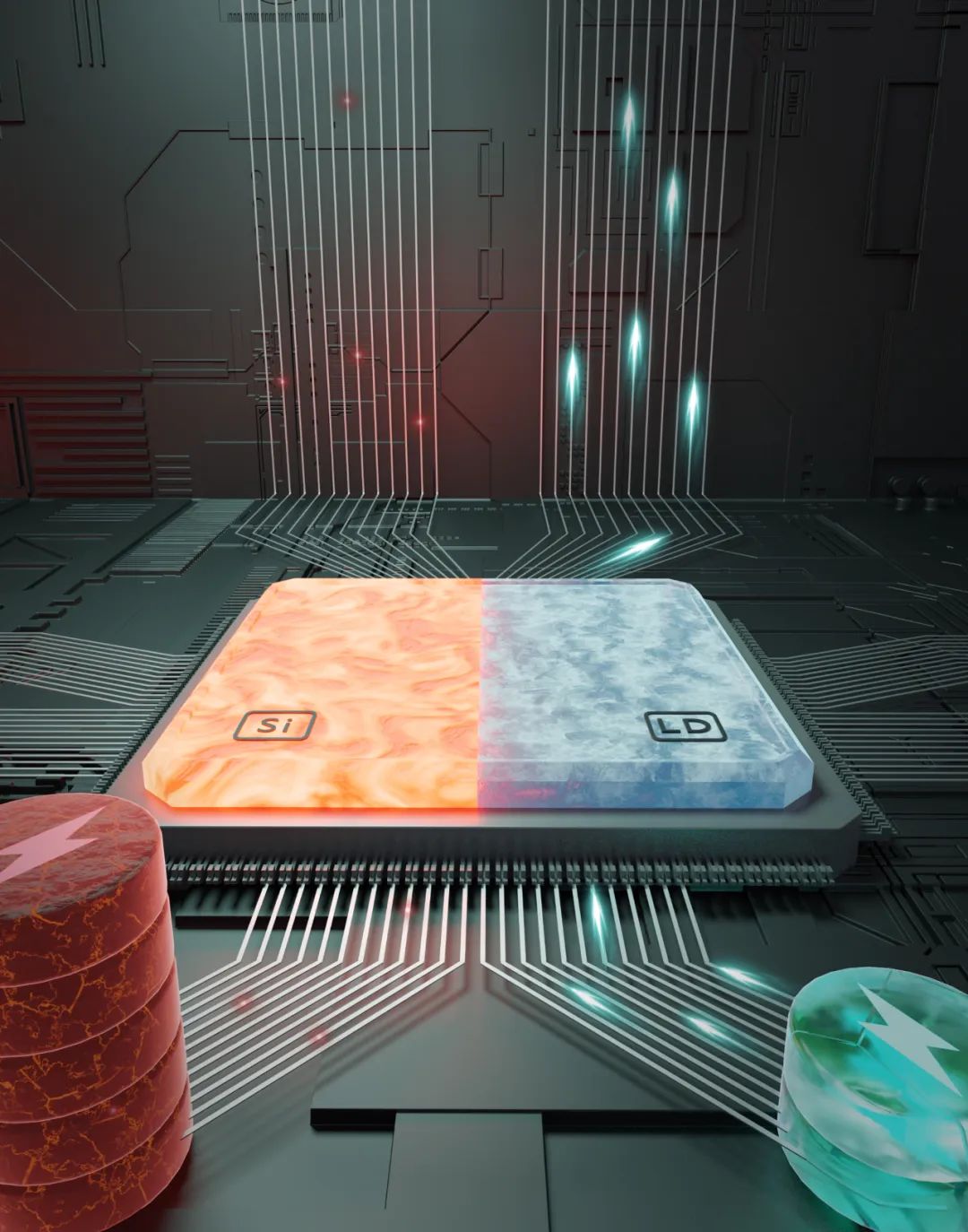

圖 展望:更快更省電的低維半導體芯片(圖片來源:北京大學)

展望

總之,本工作表明已經制造出具有歐姆接觸�����、高柵極效率和接近理想彈道比的超尺寸高性能InSe FETs���,首次證實了2D FETs可以提供接近理論預測的實際性能��,是未來?節點上硅FETs的強大競爭對手���。這項工作突破了長期以來阻礙二維電子學發展的關鍵科學瓶頸����,將n型二維半導體晶體管的性能首次推近理論極限,率先在實驗上證明出二維器件性能和功耗上優于先進硅基技術����,為推動二維半導體技術的發展注入強有力的信心和活力����。Jianfeng Jiang, et al. Ballistic two-dimensional InSe transistors. Nature, 2023.DOI:10.1038/s41586-023-05819-w

彭練矛教授

中國科學院院士�,北京大學電子學院院長。1994年獲首批國家杰出青年科學基金資助����,1999年入選首屆教育部“長江學者獎勵計劃”特聘教授���。長期從事碳基電子學領域的研究�����,做出一系列基礎性和開拓性貢獻���。四次擔任國家“973計劃”���、重大科學研究計劃和重點研發計劃項目首席科學家�����。在《科學》《自然》等期刊發表SCI論文400余篇�。相關成果獲國家自然科學二等獎(2010和2016年)����、高等學校科學研究優秀成果獎(科學技術)自然科學一等獎(2013年)�、北京市科學技術一等獎(2004年)�����,入選中國科學十大進展(2011年)、中國高等學校十大科技進展(2000和2017年)��、中國基礎科學研究十大新聞(2000年)��。個人獲何梁何利基金科學與技術進步獎(2018年)����、全國創新爭先獎(2017年)�、推動“北京創造”的十大科技人物(2015年)、全國優秀博士學位論文指導教師(2009年)、北京大學首屆十佳導師(2013年)等榮譽����。

邱晨光研究員

北京大學電子學院研究員�,“博雅青年學者”��。國家基金委“優青”(2021)、國家重點研發計劃青年首席科學家(2021)�����、KJW 173 JCJQ 首席科學家(2022)���。從事納米電子器件方面研究��,在Nature, Science, Nature Electronics, Nature Nanotechnology, ACS Nano, Nano Letters, IEDM等頂級國際期刊和會議上發表論文; 以第一作者和通訊作者在《科學》上發表論文兩篇�����,在《自然》上發表論文一篇。Science論文“5納米柵長碳納米管晶體管”實現了晶體管開關的量子極限,入選ESI高被引用論文和熱點論文�����,入選2017年中國高校十大科技進展,2017年中國100篇國際高影響論文。Science論文“狄拉克冷源晶體管”首次在國際上提出并實現冷源亞60超低功耗新器件機制���,拓寬了超低功耗器件領域范圍,入選2018全國科創中心重大標志性原創成果。Nature論文“彈道InSe晶體管”研制出世界上迄今彈道率最高、速度最快����、功耗最低的二維晶體管�����,性能超過硅基極限。

北京大學電子學院博士研究生,師從彭練矛教授與邱晨光研究員���。從事二維電子器件的極限性能的探索與器件物理研究,致力于開發超越硅基極限的后摩爾新型電子技術。在Nature�����,Nano Letters等國際知名雜志上以第一作者身份發表論文九篇��,博士期間針對二維電子學領域的關鍵科學瓶頸和底層科學問題進行攻關,實現了近彈道輸運的高速二維晶體管,性能和功耗均優于商用硅基先進技術節點��。曾獲省級優秀畢業生��、研究生“校長獎”���、研究生國家獎學金等榮譽�����。香港大學研究助理教授。2020年于北京大學信息科學技術學院取得理學博士學位���。從事后摩爾未來節點納米器件結構和物理研究,以及鋰離子電池電化學模型研發���。在Nature,Science�����,Nature Electronics���,Nature Communication���,Science Advance��,IEEE Transactions on Electron Device��,Applied Physics Letters,IEDM等國際知名雜志和會議上發表學術成果四十余篇����。系統研究了低維材料器件的建模方法,包括緊湊模型���、TCAD數值模擬及基于密度泛函的第一性原理計算。利用緊湊模型首次研究頂柵碳納米管器件彈道率�,在理論上證明了狄拉克源具有跨導增強的特性����,利用TCAD數值模擬設計新型抑制雙極性輸運器件結構���,基于第一性原理系統研究了二維材料的去釘扎歐姆接觸和器件性能極限等若干關鍵科學問題��,專注于探索后摩爾先進節點器件的底層物理�。課題組常年招收博士后與博士生����,歡迎有微電子,電子�,物理�����,化學,材料背景的有志之士加入課題組??芍苯勇撓登癯抗庋芯繂T(email:chenguangqiu@pku.edu.cn)投遞簡歷