特別說明:本文由學研匯技術 中心原創撰寫,旨在分享相關科研知識。因學識有限,難免有所疏漏和錯誤,請讀者批判性閱讀,也懇請大方之家批評指正。

原創丨彤心未泯(學研匯 技術中心)

編輯丨風云

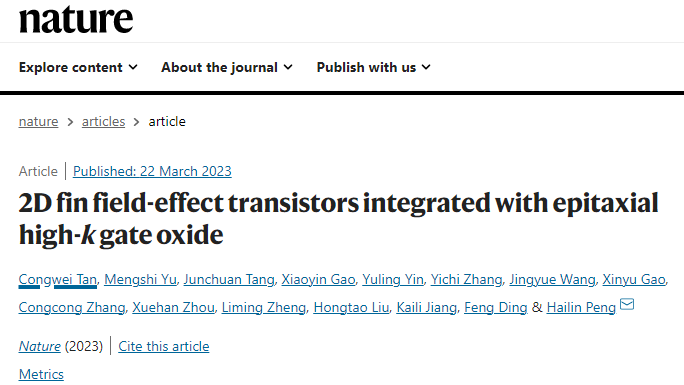

集成電路技術的進步依賴于遵循摩爾定律的互補金屬氧化物半導體(CMOS)晶體管尺寸的持續微縮。作為主要的器件結構,由垂直鰭狀通道和高k氧化物介質集成的Si鰭狀氧化物異質結構推動了CMOS向7納米和5納米技術節點的擴展。對于即將到來的5納米以下節點,這種架構具有制造垂直柵極全能(VGAA)晶體管或垂直傳輸場效應晶體管(VTFET)的潛力,以進一步提高器件性能、能源效率和集成密度。

然而,集成電路的進一步發展存在以下問題:

1、5 nm技術節點存在器件性能差的問題

在如此小的通道尺寸下,超薄Si鰭狀氧化物異質結構中厚度波動引起的界面散射極大地降低了器件性能。

2、芯片尺寸微縮逐漸逼近硅基材料物理極限

5納米以下的內在限制和不完善的界面阻礙了Si晶體管的可持續降尺度,短溝道效應和熱效應日趨顯著,新材料、新架構和新器件的探索與研究迫在眉睫。

3、新材料、新器件和新架構的開發有望突破芯片功耗和算力瓶頸

探索“后摩爾時代”新材料、新器件和新架構,有望推動高端電子器件與集成電路芯片的可持續發展。關鍵創新需要探索具有超薄高遷移率半導體通道和高k介電集成的新材料和架構。

有鑒于此,北京大學彭海琳教授課題組報道了2D鰭式-氧化物異質結構垂直排列陣列的外延合成,這是一種新型的3D結構,其中高遷移率2D半導體鰭式Bi2O2Se和單晶高k柵氧化物Bi2SeO5外延集成。2D鰭式-氧化物外延異質結構具有原子級的界面和超薄的鰭片厚度,可達一個晶胞單元(1.2 nm),實現了單取向陣列的晶圓級、位點特異性和高密度生長。基于Bi2O2Se/Bi2SeO5外延異質結構的二維鰭式場效應晶體管具有高達270 cm2V?1s?1的高電子遷移率、約1 pA μm?1的超低態電流、高達108的高通流比和高達830 μA μm?1的高通流電流,在400 nm通道長度上滿足國際器件與系統路線圖(IRDS)的低功耗要求。二維鰭式-氧化物外延異質結構為摩爾定律的進一步推廣開辟了新的途徑。

技術方案:

1、實現了2D層狀鰭片陣列與高k環柵氧化物集成

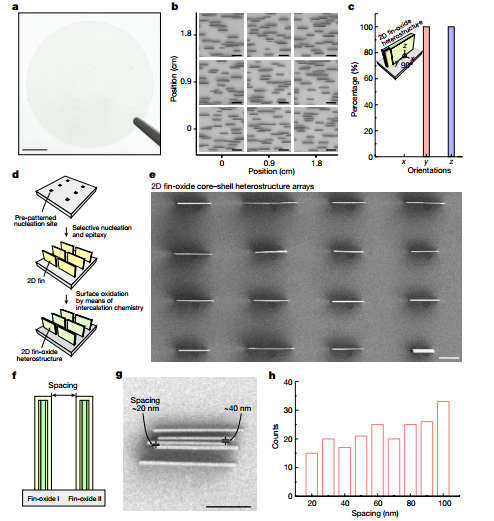

作者選擇Bi2O2Se作為2D鰭片通道,與高k的氧化物Bi2SeO5,采用雙外延策略,在市售絕緣襯底上合成了晶圓級、排列良好的2D Bi2O2Se/Bi2SeO5鰭狀氧化物異質結構陣列。

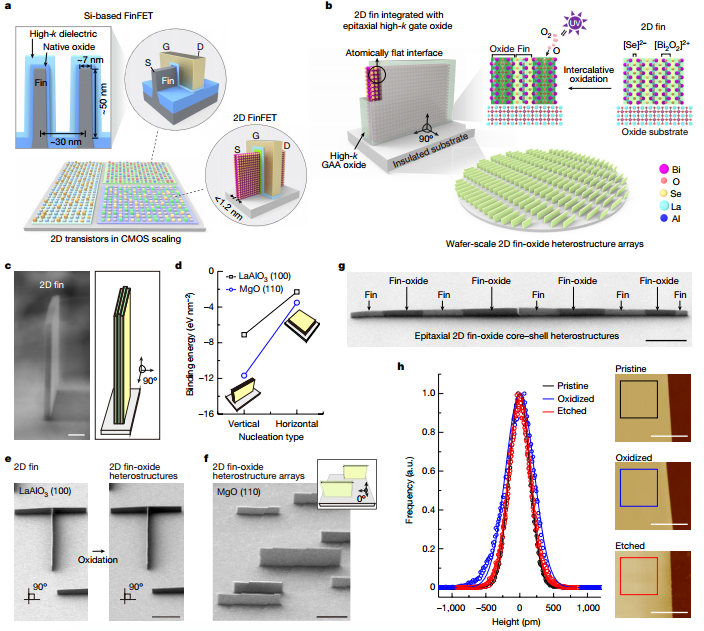

2、表征了二維鰭狀氧化物異質結的微觀結構

作者通過多種表征手段耦合,探究了二維鰭狀氧化物異質結構的原子分辨率界面微觀結構,并闡明了微觀原子結構與其性能的構效關系。

3、實現了二維鰭狀氧化物異質結構陣列的定向集成

通過控制成核位點,作者成功地在襯底的指定位置制備了單個二維鰭狀氧化物異質結構的單向周期性陣列,實現了約100nm到約20nm的小間距。

4、探究了2D FinFETs的電學性能

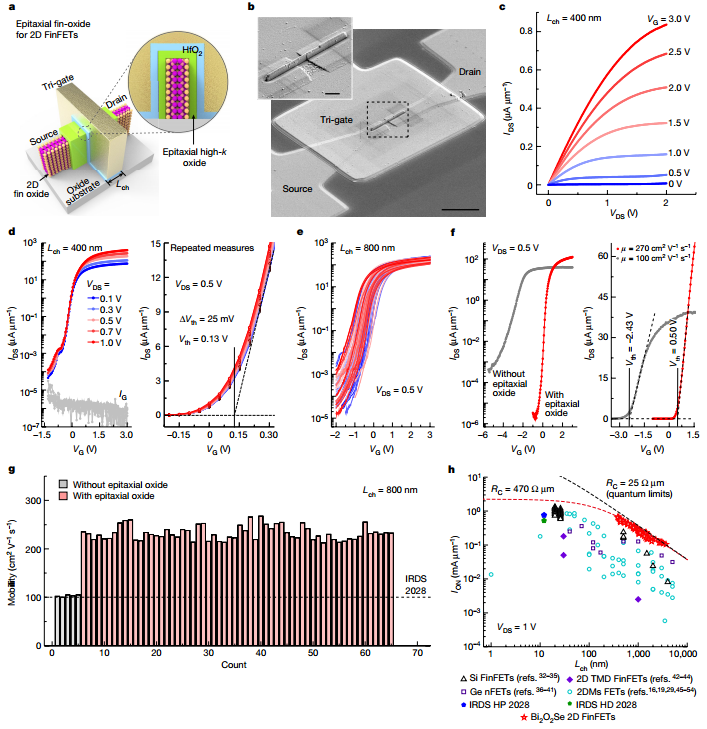

作者制備并優化了垂直二維Bi2O2Se/Bi2SeO5/HfO2 FinFETs,證實了通道長度為400 nm的二維FinFET具有良好的靜電控制性能以及設備的可靠運行。

技術優勢:

1、首次實現了二維半導體鰭片/高κ柵氧化物異質結陣列集成

作者報道了世界首例二維半導體鰭片/高κ柵氧化物異質結陣列的外延生長及其三維架構的異質集成,首次實現了溝道厚度約6納米的高性能二維垂直鰭式晶體管的研制。

2、實現了超薄Bi2O2Se鰭片與具有原子平面界面的高k氧化物的完美集成

作者在不同絕緣襯底上垂直放置的2D鰭狀氧化物異質結構陣列的晶圓級外延,超薄的高遷移率2D Bi2O2Se翅片與具有原子平面界面的外延單晶2D高k氧化物Bi2SeO5層完美集成。

3、獲得了可同時滿足國際器件與IRDS的高性能低功耗晶體管

二維FinFET在遷移率(270 cm2/Vs)、關態電流(1 pA/μm)和開關比(108)等性能滿足業界高性能低功耗器件要求的同時,相對于商用Si、Ge及過渡金屬硫化物等溝道材料,在開態電流密度方面展現出二維FinFET電子學的優勢。

2D層狀鰭片陣列與高k環柵氧化物集成

作者選擇Bi2O2Se作為2D鰭片通道,不僅是因為其獨特的層狀結構、超高的載流子遷移率、適度的帶隙和出色的穩定性,還因為它有一個高k (k≈21)的原生氧化物配合物Bi2SeO5,這是高性能2D電子器件制造和集成的關鍵。采用雙外延策略,在市售絕緣襯底上合成了晶圓級、排列良好的2D Bi2O2Se/Bi2SeO5鰭狀氧化物異質結構陣列。通過SEM表征了其微觀結構,并用熱力學方法測定了二維層狀Bi2O2Se翅片在絕緣氧化物襯底上的垂直外延,實驗結果表明,在二維材料外延理論的指導下,通過調節襯底的對稱性可以控制垂直二維Bi2O2Se的對準。

圖 2D層狀鰭片陣列集成了高k環柵氧化物

結構表征

為了進一步顯示二維鰭狀氧化物異質結構的原子分辨率界面微觀結構,對異質結構/LaAlO3薄片進行了AC-STEM研究,結果表明其高度約為400 nm,翅片厚度約為6.1 nm,原生氧化物厚度約為7 nm。外延層狀氧化物外殼完全包裹二維層狀鰭狀核,顯示出矩形形態和優異的成分均勻性。HR-STEM圖像表明,LaAlO3(100)襯底表面的外延2D Bi2O2Se/Bi2SeO5鰭氧化物異質結構具有原子鋒利的界面和良好的點陣匹配。

圖 二維層狀鰭狀氧化物外延異質結構的結構表征

定向集成二維鰭狀氧化物異質結構陣列

對于未來的集成電路,晶圓級二維鰭片陣列和高k氧化物介電集成的穩定制備是不可避免的二維Bi2O2Se/Bi2SeO5鰭狀氧化物異質結構陣列外延形成在1英寸MgO(110)晶圓上,錯切角小于0.1°。從晶圓不同位置獲得的SEM圖像顯示垂直排列的二維鰭狀氧化物異質結構具有相同的方向,這與晶圓尺度上的外延性質一致。單定向陣列的特定位置和高密度增長對于實現批量制造和緊湊集成至關重要。通過控制成核位點,作者成功地在襯底的指定位置制備了單個二維鰭狀氧化物異質結構的單向周期性陣列。預制的成核位點提供了具有較低成核能勢能的邊緣,從而錨定了對準的二維核,用于二維鰭狀陣列的外延。二維鰭狀氧化物納米結構的單向對齊可行地實現了約100nm到約20nm的小間距。通過優化的高分辨率光刻技術,可以制備滿足先進技術節點要求的高密度二維鰭狀氧化物異質結構陣列。

圖 定向二維鰭狀氧化物異質結構陣列的精確集成

電學性能

作者制備了垂直二維Bi2O2Se/Bi2SeO5/HfO2 FinFETs,溝道長度約為400 ~ 3700 nm。采用傳輸線方法計算了2D FinFETs的合理低接觸電阻約470 Ω μm。優化后的2D Bi2O2Se/Bi2SeO5/HfO2 FinFET在一個由7nm厚外延高k介質Bi2SeO5和7nm厚HfO2包圍的鰭片溝道中,長度為400nm,厚度為6.1 nm,高度約為400nm。通道長度為400 nm的二維FinFET具有良好的靜電控制性能,在VDS為2 V、VG為3 V時,其低通流密度<0.1 nA μm?1,大通流比>107,高通流密度可達830 μA μm?1。此外,在進行50次重復掃描測試后,增強模式2D Bi2O2Se/Bi2SeO5/HfO2 FinFET的正閾值電壓為0.13 V,傳輸曲線略有偏移(約0.025 V),驗證了設備的可靠運行。

圖 二維氧化物鰭片異質結構的電學性能

總之,本文提出的集成外延單晶高k Bi2SeO5電介質的晶圓級2D Bi2O2Se鰭片陣列滿足了未來先進晶體管的最嚴格要求,包括單向取向、大面積、位置選擇和高密度生長、超高展弦比、原子平面界面、1.2 nm尺度的超薄體、高載流子遷移率和高導通電流密度。隨著進一步優化,在工業兼容的介電襯底(例如,CaF2/Si和MgO/Si)上實現高密度垂直2D鰭狀氧化物異質結構陣列的精確位置生長,超尺度2D finfet和VGAA FETs將實現進一步的晶體管縮放,并可能擴展摩爾定律。

參考文獻:

Tan, C., Yu, M., Tang, J. et al. 2D fin field-effect transistors integrated with epitaxial high-k gate oxide. Nature (2023).

https://doi.org/10.1038/s41586-023-05797-z