特別說明:本文由學研匯技術中心原創撰寫,旨在分享相關科研知識。因學識有限,難免有所疏漏和錯誤,請讀者批判性閱讀,也懇請大方之家批評指正。

原創丨彤心未泯(學研匯 技術中心)

編輯丨風云

學習對于邊緣智能設備適應不同的應用場景和用戶來說非常重要。當前訓練神經網絡的技術需要在計算和存儲單元之間移動大量數據,這阻礙了在邊緣設備上實現學習。相比之下,基于憶阻器的神經啟發計算通過其顛覆性的內存計算架構和模擬計算范式消除了這種廣泛的數據移動。

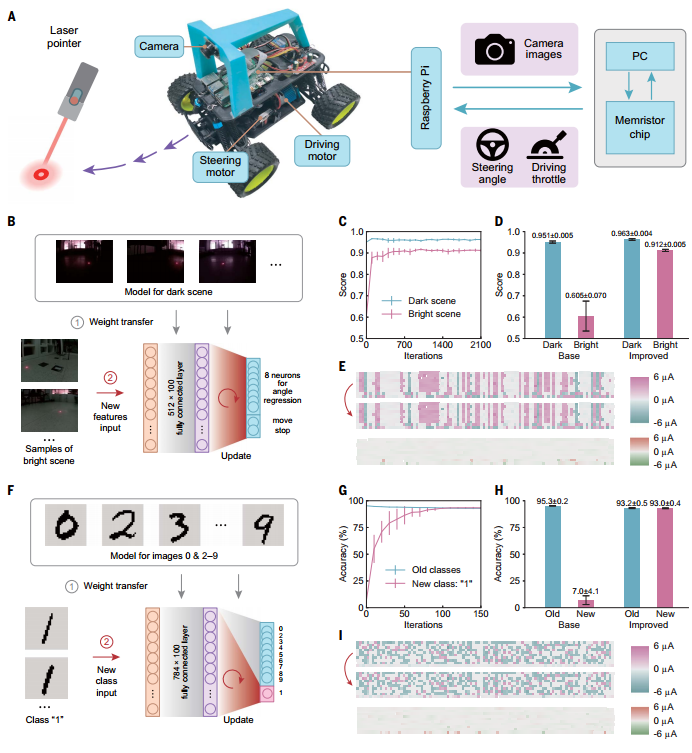

有鑒于此,清華大學吳華強、高濱等人開發了一種具有改進的學習能力和低能耗的全集成憶阻器芯片,提出了基于憶阻器的符號和閾值學習(STELLAR)架構。 STELLAR架構中包括其學習算法、硬件實現和并行電導調諧方案,都是通過使用憶阻器交叉陣列來促進片上學習的通用方法,而不考慮憶阻器器件的類型。所制造的神經啟發計算芯片集成了兩個憶阻器交叉陣列(總共約160000個單元)和所有必要的電路模塊。根據獲得的硬件測量結果,憶阻器芯片的能耗比基于數字加速器的系統低35倍。作者演示了多項改進學習任務,包括運動控制、圖像分類和音頻識別。基于憶阻器的神經計算芯片可以促進邊緣人工智能設備的開發,以適應新的場景和用戶。

邊緣學習

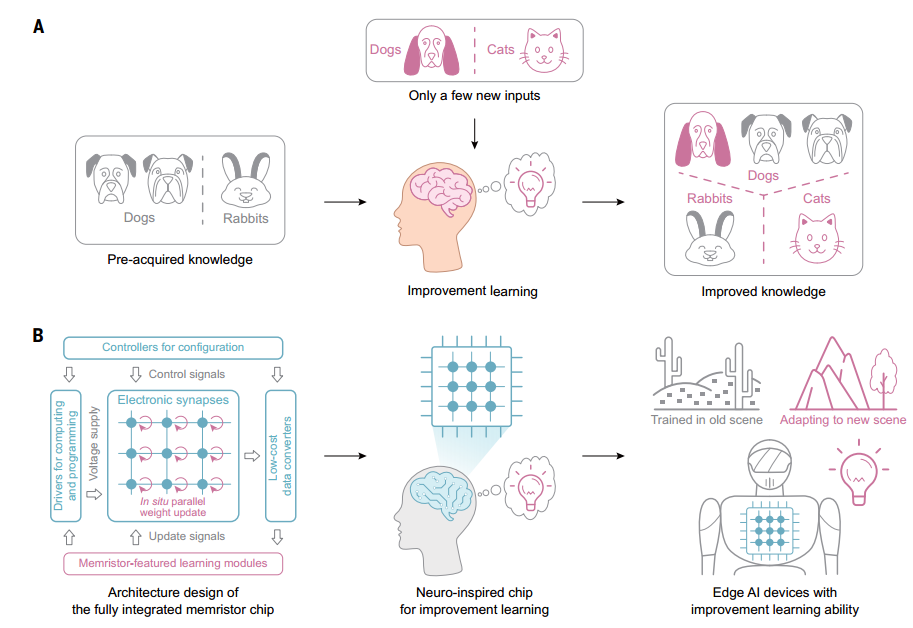

作者展示了一種基于憶阻器的神經啟發計算芯片,該芯片能夠實現完全學習,并為此提出了基于憶阻器的符號和閾值學習(STELLAR)架構。在該架構中,首先提出了芯片內更新方案來調整憶阻器,節省了電導調諧操作中過多的寫入和讀取成本。其次,芯片內計算模塊旨在確定權重更新方向,該過程僅涉及輸入、輸出和誤差的符號,而不涉及其高精度格式。第三,提出了循環并行電導調諧方案,該方案進一步減少了引起的能耗和延遲,并適應了憶阻器的有限耐用性。

圖 使用受神經啟發的憶阻器芯片進行邊緣學習

用于芯片內學習的憶阻器架構

作者提出了STELLAR架構以可觀的能源效率、面積效率和準確性支持芯片內的學習。通過該方案可以避免復雜的精確權值更新計算和寫入驗證過程以及復雜的外圍電路設計,從而實現節能的硬件。在保持幾乎相同的精度的情況下, STELLAR架構的能耗比傳統BP方法低了兩個數量級。此外,作者還提出了一種循環并行電導調諧方案,由于在每次芯片內學習迭代期間僅更新一半的憶阻器器件,循環并行電導調諧方案減少了感應能耗并減輕了對憶阻器耐久性的要求。

圖 用于芯片學習的憶阻器架構設計

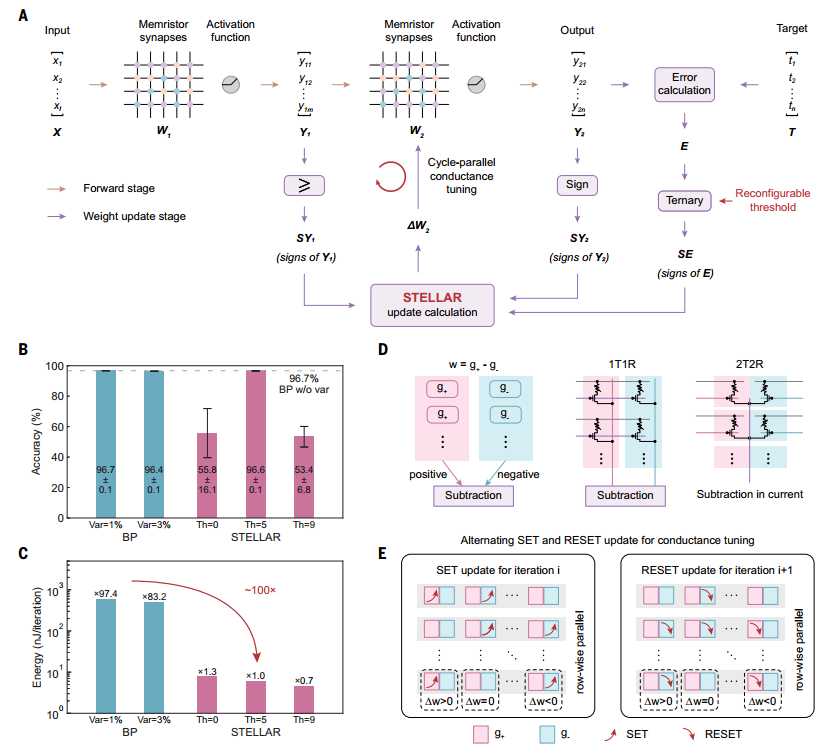

芯片設計、制造和測量

作者詳細展示了STELLAR 架構的整體電路實現和所制造芯片的顯微照片。憶阻器器件使用TiN/HfOx/TaOy/TiN材料堆疊,并且制造工藝與標準CMOS工藝兼容。因此,憶阻器可以方便地與復雜的CMOS電路集成,以產生出色的收率(所有160000個單元幾乎100%)。作者評估了電導波動對芯片精度的影響,表明了芯片的穩定性。還演示了憶阻器芯片的實時手寫數字識別和MNIST圖像分類,證實了該芯片的學習能力。然后,利用硬件測量結果評估了芯片內學習的能耗,表明通過優化 ADC 設計可以進一步降低能耗。

圖 用于芯片學習的憶阻器芯片

芯片內改進學習

作者利用憶阻器芯片進一步演示了四個改進學習任務,包括學習新樣本的運動控制任務、音頻識別任務、圖像分類任務和新類別的運動控制任務。結果表明,只需少量新輸入即可快速實現新知識的學習,且這種學習是在不丟失預先獲得的知識的情況下完成的。所提出的 STELLAR 架構可以擴展到更大的神經網絡,并且可以實現具有高精度軟件精度的高效改進學習。

圖 憶阻器芯片的改進學習演示

參考文獻:

WENBIN ZHANG, et al. Edge learning using a fully integrated neuro-inspired memristor chip. Science, 2023, 381(6663):1205-1211.

DOI: 10.1126/science.ade3483

https://www.science.org/doi/full/10.1126/science.ade3483