研究背景

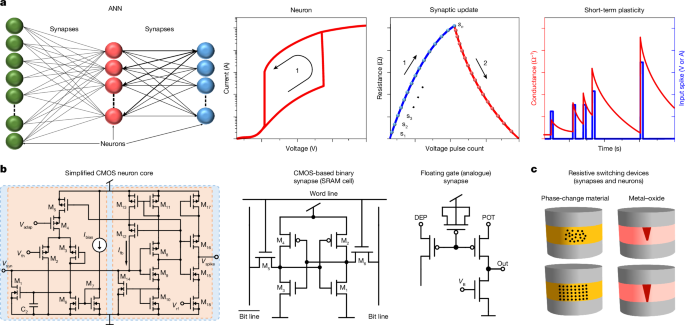

人工神經網絡(ANN)是一種仿生計算系統,由于其能夠在同一位置同時進行計算和存儲,避免了數據傳輸帶來的能量消耗和延遲,因此被廣泛應用于人工智能、圖像識別和自動駕駛等領域。與傳統的基于馮·諾依曼架構的計算機相比,ANN 在能耗和計算效率上具有顯著優勢。然而,傳統的互補金屬氧化物半導體(CMOS)晶體管難以同時實現神經元和突觸功能,因此需要額外的電路設計,導致硬件成本高、集成度受限。此外,憶阻器等新興材料雖在神經形態計算方面展現出潛力,但其集成難度大、可靠性不足,因此帶來了實際應用的挑戰。

針對這一挑戰,新加坡國立大學Mario Lanza教授課題組在“Nature”期刊上發表了題為“Synaptic and neural behaviours in a standard silicon transistor”的最新論文。該團隊設計了一種基于標準體硅金屬氧化物半導體場效應晶體管(MOSFET)的新型神經元和突觸仿生器件,實現了低成本、高集成度的神經形態計算單元。研究人員通過將 MOSFET 工作于接近穿透狀態,并調節體連接電阻(RB),成功模擬了生物神經元的泄漏-積分-發放(LIF)行為以及突觸的長期和短期可塑性。

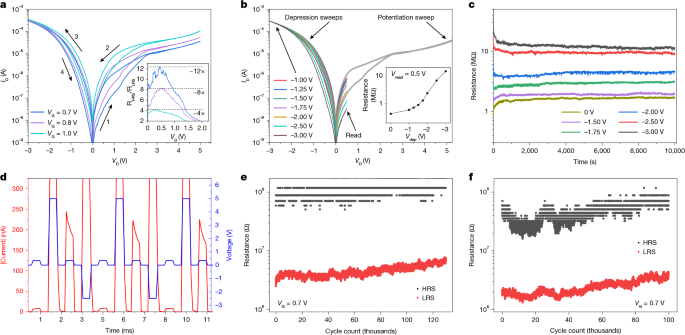

利用這種獨特的偏置方式,顯著提高了器件的動態范圍(超過 103)、開關斜率(低于 10?mV/dec)和耐久性(超過 1000 萬次循環)。實驗結果表明,該器件能夠在單個 MOSFET 結構內穩定存儲至少六種突觸權重,并在 70 萬次突觸增強和抑制循環中保持高穩定性。這一研究為人工神經網絡的硬件實現提供了新的思路,推動了高效、低功耗神經計算的發展。

研究亮點

(1) 實驗通過對標準體硅 MOSFET 施加特定(非傳統)偏置,實現了單個 CMOS 晶體管同時表現出神經元和突觸行為,得到了優異的仿生電子神經元和突觸特性。

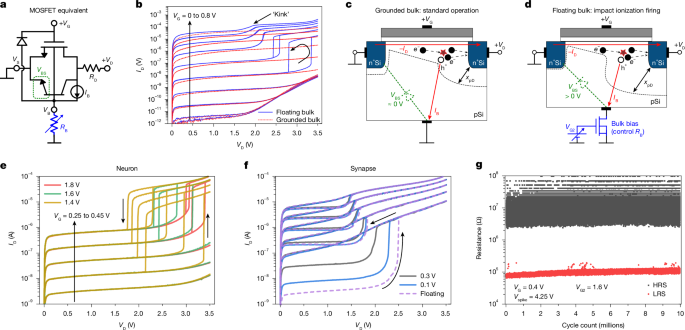

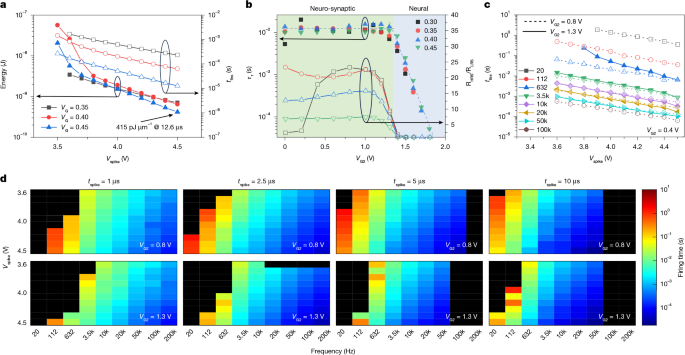

(2) 實驗通過將 MOSFET 工作在接近穿透條件的狀態,并調節體連接到地的電阻(RB),構建了兩晶體管單元(NS-RAM 單元),得到了可連續調節的神經-突觸行為,在電路層面上展現出極高的靈活性。

(3) 在神經元模式下,NS-RAM 單元能夠模擬泄漏-積分-發放(LIF)神經元行為和自適應頻率突發,表現出高開關斜率(低于 10 mV/dec)、寬動態范圍(超過 103)、高耐久性(超過 1000 萬次循環)和低功耗(發放能量低至 415 pJ/μm)。

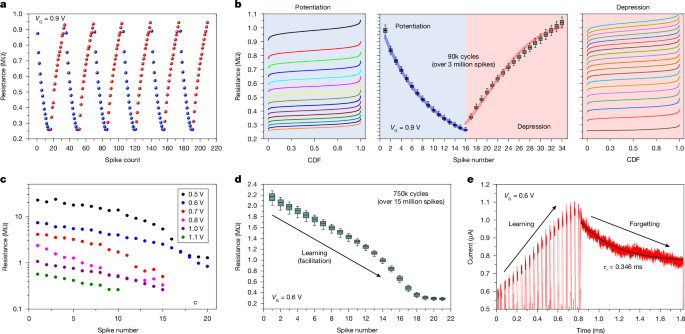

(4) 在突觸模式下,單個 MOSFET 在浮體配置下可被編程為至少六個穩定的突觸權重(長期增強和抑制),耐久性超過 10? 次循環,并表現出短時脈沖增強、抑制和突觸可塑性,在 70 萬次增強/抑制循環中保持 14 個不同的權重水平,具有低變異性和高穩定性。

圖文解讀

圖1:晶體管及其在神經突觸模擬裝置中的應用。

圖2: 浮體floating-bulk n-溝道180nm MOSFET的準穩態I–V特性,驗證了神經突觸能力。

圖3:在浮體180nm MOSFET中,用穿通控制調節神經行為。

圖4:500nm浮體MOSFET的突觸可塑性。

圖5:500nm浮體MOSFET的長期突觸行為

結論展望

標準n型MOSFET在浮體條件下運行時,能夠模擬多種神經-突觸行為,并展現出高性能、良好的能效、低變異性、高可調性和低面積占用。由于驅動這些行為的所有過程均由半導體中的電荷分布控制(無論是否涉及電荷俘獲),該器件在所有工作模式下均表現出極高的穩健性。

盡管在微秒級脈沖工作模式下,器件的工作電壓(3.6至4.5V)相較于標準CMOS晶體管較高,但與憶阻器及其他新興器件相比仍具有競爭力。然而,穿透雪崩效應在正常工作條件下是一種寄生效應,可通過特定的器件工程手段(如摻雜工藝或阻止層)加以抑制。因此,可以通過優化器件參數來提升特定性能指標(包括工作電壓)。研究表明,在溝道長度LCH=180 nm的MOSFET中觀察到的神經-突觸行為,同樣可在LCH=500 nm的MOSFET中復現,并且其工作電壓仍處于標稱范圍(5.5V),表明這些行為受相同的基本物理機制驅動。因此,該工作模式不會對器件可靠性構成威脅。

本研究結果凸顯了一種極為簡單緊湊的NS-RAM單元,可高效模擬多種神經-突觸行為。在神經元方面,除了閾值電壓調制外,還可以通過控制體偏置網絡來調節不應期、興奮或抑制信號的敏感度,并適應脈沖頻率變化。同一電路單元可在電流模式或電壓模式下運行,提供快速的泄漏-積分-發放行為,或在不同神經網絡架構中作為雙端、三端或四端神經元使用。此外,該器件可通過控制體偏壓脈沖來接收外部復位信號。在突觸方面,單個MOSFET可取代傳統的靜態隨機存取存儲器(SRAM),或在多級突觸存儲陣列中替代嵌入式閃存,從而大幅降低每位存儲單元的面積和成本。此外,若使用金屬氧化物高k介質(如HfOx),MOSFET的突觸行為或可進一步增強,因為這類材料的電荷俘獲與釋放能力遠超本研究中使用的SiO?。同時,浮體MOSFET的長時間狀態保持能力,使其可應用于計算存儲一體化架構,并在動態隨機存取存儲器(DRAM)中提供較長的突觸權重保持時間,從而顯著降低訪問延遲。

相比其他新興器件,該方法的一大優勢在于,MOSFET神經元和突觸能夠直接應用于標準CMOS設計流程,并可通過物理建模或緊湊建模技術進行模擬分析。目前,基于長時突觸特性的人工神經網絡(ANN)已有較成熟的設計和實現方法,而基于短時神經-突觸特性的神經網絡仍缺乏完善的計算模型和算法。為此,研究團隊成功利用開源SPICE仿真器,結合基本的MOSFET與雙極晶體管模型,對雪崩模式進行了精確建模,并獲得了與實驗數據高度一致的靜態與動態特性。這一方法將有助于快速實現復雜系統設計與仿真。

在微電子技術發展史上,不同類型的器件和電路均曾展現出神經元和突觸特性。然而,從首次實現單個神經元或突觸行為到硬件人工神經網絡(ANN)真正落地,通常需要至少七年時間,甚至某些器件(如鐵電FET)至今尚未實現這一目標。這是因為,從單個器件到完整ANN的實現,需要經歷大量定制外圍電路開發、測試接口設計、系統級集成、工藝迭代與優化。而采用非常規偏置的MOSFET來模擬神經-突觸行為,或可成為推動下一代神經形態計算的重要突破點,無需對現有CMOS技術進行重大變更。MOSFET的潛力仍在不斷被挖掘,本研究進一步證明了它是實現ANN硬件的理想基礎單元。

原文詳情:

Pazos, S., Zhu, K., Villena, M.A. et al. Synaptic and neural behaviours in a standard silicon transistor. Nature (2025).

https://doi.org/10.1038/s41586-025-08742-4