隨著晶體管尺寸的持續微縮,傳統MOSFET器件面臨的功耗問題已成為制約集成電路發展的重要瓶頸。在這一背景下,負電容晶體管(NC-FET)通過在柵極中引入鐵電材料,理論上能夠突破玻爾茲曼極限,實現室溫下晶體管亞閾值擺幅(SS)<60mV/dec的超低功耗特性,被認為是未來CMOS器件最具發展潛力的研究方向之一。然而,現有NC-FET普遍存在回滯效應和鐵電層微縮難題,制約了其實際應用。同時,以二硫化鉬(MoS2)為代表的新型溝道材料,憑借其優異的短溝道效應抑制能力、高遷移率、柵控能力以及良好的CMOS工藝兼容性,成為未來晶體管技術的重要溝道候選材料。

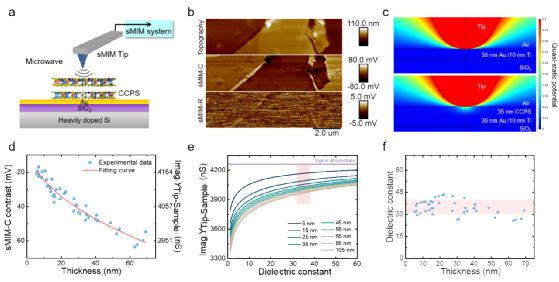

近日,上海交通大學王林團隊在國際知名學術期刊《Advanced Materials》上發表題為“Van der Waals Ferroelectric CuCrP2S6-Enabled Hysteresis-Free Negative Capacitance Field‐Effect Transistors”的研究論文。團隊采用掃描微波阻抗顯微鏡(sMIM)技術對范德華鐵電材料CuCrP2S6(CCPS)進行表征分析,揭示了其在納米尺度下的高介電常數(~35)以及隨厚度變化的不敏感性。在此基礎上,采用MoS2作為溝道材料構建制備了NC-FET。通過深入研究器件結構中鐵電層與溝道層的電容匹配關系,精確設計并優化各部分厚度,實現了與掃描速率/范圍無關的零回滯NC-FET技術。最后,基于該技術構建的反相器表現出0.2 V的超低工作電壓和與電壓掃描范圍無關的零回滯特性。該工作進一步拓展了鐵電材料在納米電子器件中的應用,其零回滯、低電壓的特性有望應用于存內計算、物聯網終端芯片等低功耗場景。

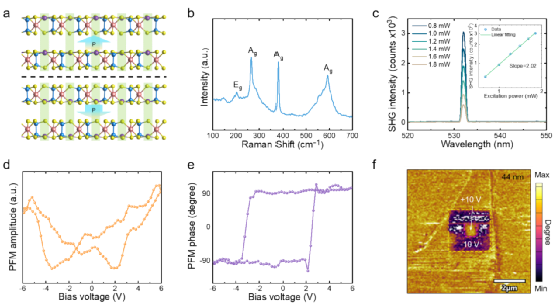

圖1、CCPS的材料特性和鐵電性表征。圖片來源:Advanced Materials

圖2、利用掃描微波阻抗顯微鏡技術表征CCPS的介電特性。圖片來源:Advanced Materials

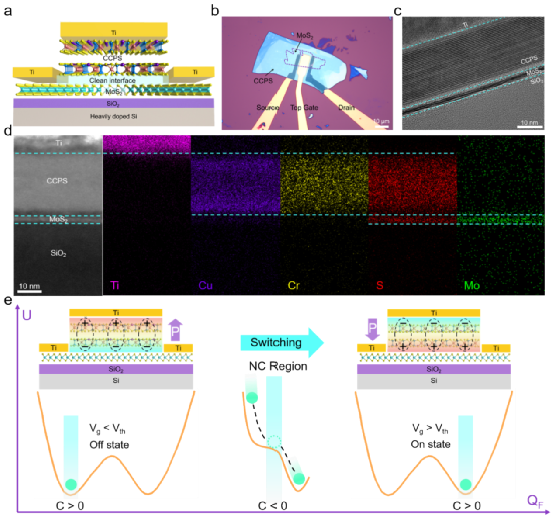

圖3、基于CCPS和MoS2的NCFET構筑。圖片來源:Advanced Materials

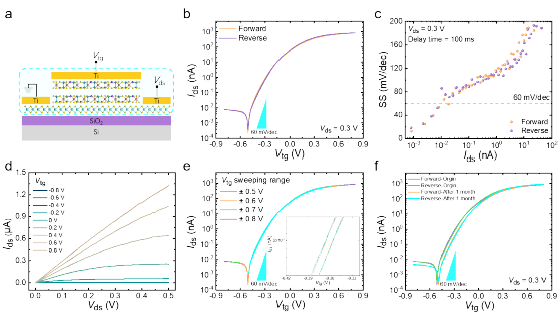

圖4、基于CCPS的零回滯MoS2 NCFET電學特性表征。圖片來源:Advanced Materials

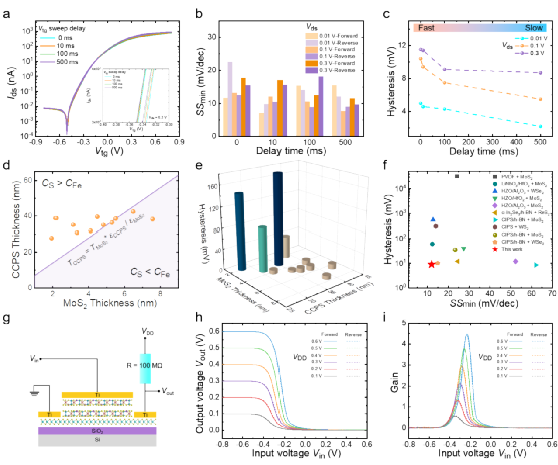

圖5、MoS2 NCFET中掃描速率的影響、電容匹配特性研究、以及低工作電壓零回滯反相器的實現。圖片來源:Advanced Materials

文章鏈接:https://doi.org/10.1002/adma.202419125

第一作者:陳瀚

通訊作者:王林

該工作得到了上海交通大學和國家自然科學基金委的支持。