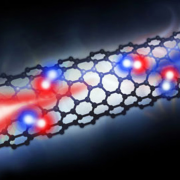

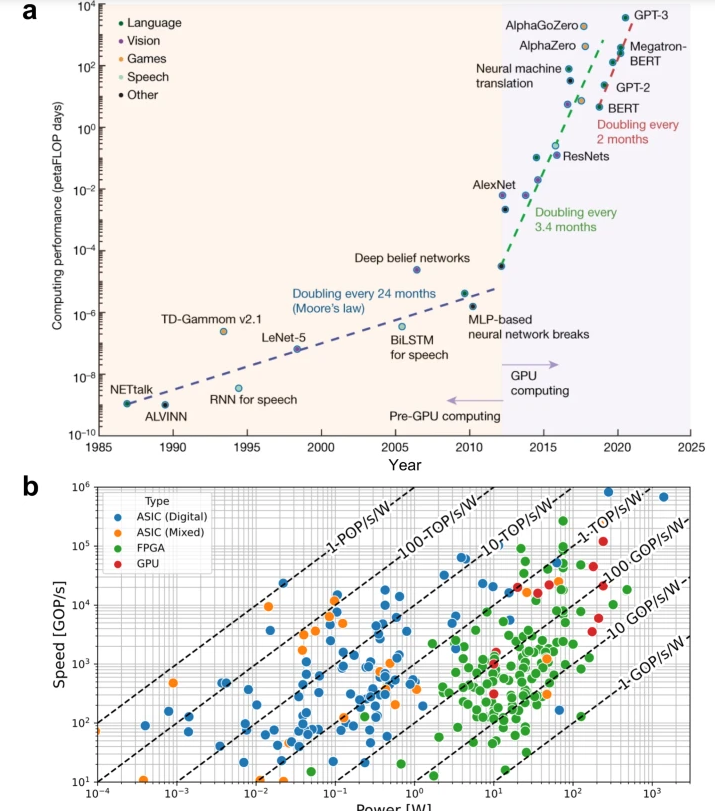

人工智能(AI)目前正經歷著由深度學習(DL)技術驅動的蓬勃發展階段,該技術依賴于并行運行連接的簡單計算單元網絡。在傳統的馮·諾依曼機器中,存儲器和處理單元之間的低通信帶寬不支持廣泛依賴于大數據集的新興應用的要求。最近的計算范式,如高并行化和近內存計算,在一定程度上有助于緩解數據通信瓶頸,但需要范式轉換的概念。憶阻器是一種超越互補金屬氧化物半導體(CMOS)技術的新型技術,由于其獨特的內在器件特性,使存儲和計算能夠在低功耗下以小模型大規模的并行占用空間,因此是存儲設備的一個很有前景的選擇。從理論上講,這直接轉化為能源效率和計算吞吐量的大幅提高,但仍存在各種實際挑戰。鑒于此,來自阿卜杜拉國王科技大學的Mario Lanza研究實現了基于硬件的憶阻人工神經網絡(ANNs)的最新成果。

文章要點:

1) 該研究詳細描述了憶阻器每個模塊的工作原理和不同的設計方案及其各自的優缺點,以及準確估計性能指標所需的工具;

2) 此外,該研究為那些打算開始在該領域工作的人和尋求整體方法的專家提供了一份關于憶阻神經網絡所涉及的材料和方法的全面協議。

參考資料:

Aguirre, F., Sebastian, A., Le Gallo, M. et al. Hardware implementation of memristor-based artificial neural networks. Nat. Commun. (2024).

10.1038/s41467-024-45670-9

https://doi.org/10.1038/s41467-024-45670-9