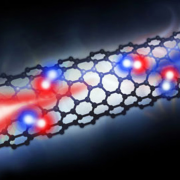

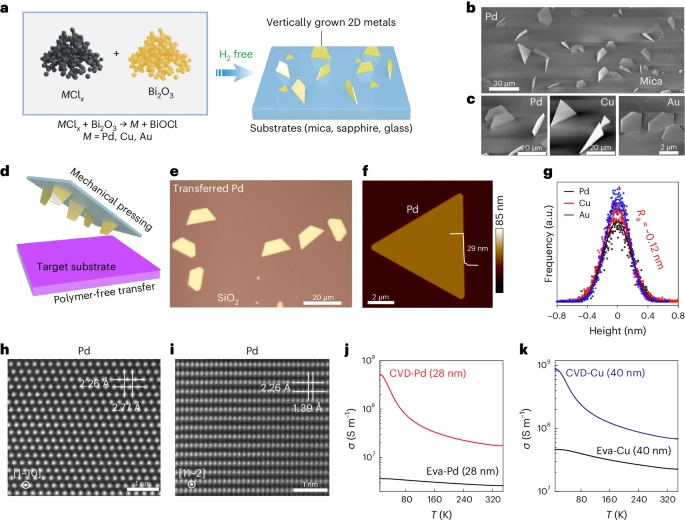

將薄原子層沉積電介質與二維(2D)半導體集成可用于制造電容等效厚度低于1nm的2D晶體管。然而,惰性表面上原子層沉積的非均勻成核以及隨后的高能金屬蒸發會使原子薄的電介質變得不絕緣。近日,來自南開大學的Jinxiong Wu等人開發了一種氧化鉍輔助化學氣相沉積方法,用于合成具有原子級平坦表面的單晶金屬納米片。

文章要點:

1) 該研究開發的方法中,納米片在基材上垂直生長,可以通過無聚合物的機械壓制輕易地轉移到目標基材上,且研究表明,鈀納米片為厚度低于3 nm的平面氧化鋁(Al2O3)和氧化鉿(HfO2)電介質的原子層沉積提供了優異的表面;

2) 此外,該研究發現,這些納米片可以層壓到幾層二硫化鉬(MoS2)上作為柵極堆疊,其電容等效厚度為0.9 nm,電容密度約為3.9μF·cm?2,這種MoS2頂部柵極晶體管具有2 nm厚的Al2O3或HfO2電介質,其漏電流為10?6 A·cm?2中,低工作電壓約為0.45 V,滯后小于1 mV。

參考資料:

Zhang, L., Liu, Z., Ai, W. et al. Vertically grown metal nanosheets integrated with atomic-layer-deposited dielectrics for transistors with subnanometre capacitance-equivalent thicknesses. Nat Electron (2024).

10.1038/s41928-024-01202-3

https://doi.org/10.1038/s41928-024-01202-3