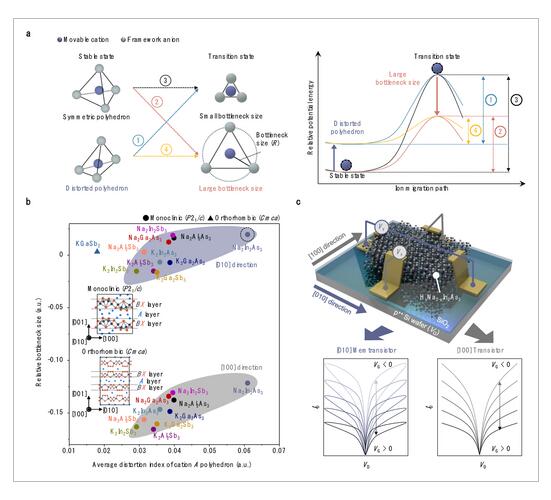

使用范德華(vdW)間隙作為離子遷移路徑,類似于鋰離子電池中的陰極材料,可以改善離子遷移。如果這些材料也具有半導體特性,它們可以同時控制電子或空穴傳輸。這種材料可用于結合存儲器和半導體特性的記憶晶體管。然而,現有的材料依賴于晶界等缺陷作為遷移路徑,導致高離子遷移能量勢壘和開關電壓。在此,延世大學Wooyoung Shim、Aloysius Soon、瓦倫西亞理工大學Juan Bisquert使用HxNa2-xIn2As3演示了膜晶體管,該膜晶體管利用vdW間隙進行離子遷移,從而降低了離子遷移的能量勢壘。

本文要點:

1) 由于較低的遷移能壘,在低對稱晶體結構中,離子遷移更容易在[010]方向上發生,而在[100]方向上則不會發生遷移,這表明了方向依賴性。這一發現為識別半導體材料中的離子遷移提供了至關重要的指導方針,否則這些遷移可能會被忽視。

2) 此外,使用vdW間隙作為遷移路徑、遷移能壘隨離子運動方向的變化及其對低功耗的影響是指導薄膜晶體管材料未來發展的關鍵因素。

Taeyoung Kim et.al Memristive InAs-Based Semiconductors with Anisotropic Ion Transport Adv. Mater. 2025

DOI: 10.1002/adma.202500056

https://doi.org/10.1002/adma.202500056